FPGA-valmistaja Xilinx esitteli tänään uuden visionsa ja samalla uuden tuotekategorian, jota se kutsuu nimellä ACAP eli adaptiivinen laskennallisen kiihdytyksen alusta. Vuoden alussa Xilinxin pääjohtajana aloittanut Victor Peng sanoo suorastaan raflaavasti, että vanhan PC-laskennan aika on ohi.

- ACAP-laskennan kyvykkyydet menevät paljon perinteisen FPGA:n kykyjä pidemmälle. Kyse on aidosti uudesta tuotekategoriasta, jota voidaan muuttaa laitetasolla sovittautumaan erilaisiin sovelluksiin ja erilaisiin työkuormiin, Peng sanoi lehdistötilaisuudessa.

Sanoille on katetta. ACAP-prosessorilla toimintoja voidaan muuttaa dynaamisesti suorituksen aikana. Muutos vie aikaa millisekunteja ja sen jälkeen uusi sovelluskohtainen laskenta onnistuu paljon suuremmalla teholla wattia kohti kuin yleiskäyttöisellä prosessorilla tai grafiikkasuorittimella.

Pengin mukaan ACAP sopii ihanteellisesti uusiin big data- ja tekoälysovelluksiin. Tällaisia ovat videon käsittely, tietokantojen käsittely, datan pakkaaminen, haut, AI-mallien laskenta, konenäkö, sekä monet verkkoprosessoinnin kiihdytysfunktiot.

Ensimmäinen ACAP-perhe on nimeltään Everest ja se toteutetaan TSMC:n 7 nanometrin prosessissa. Piille ensimmäiset sirut ovat ehtimässä jo tämän vuoden aikana. - Everest-piirit tulevat eroamaan radikaalisti siitä, mitä Xilinx ja esimerkiksi Altera ovat tähän asti tehneet. Kyse on teknologisesta murroksesta koko alalla, Peng hehkuttaa.

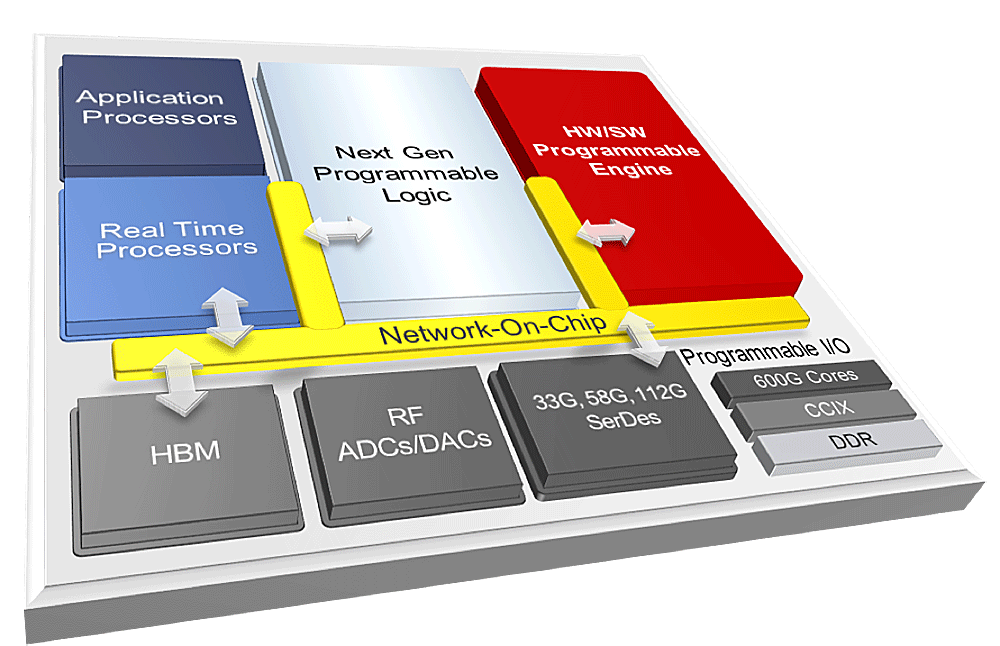

ACAP on uudenlainen FPGA-matriisi, jossa on kovakoodattuja DSP-lohkoja, jaettu muistijärjestelmä, moniytiminen järjestelmäpiiri ja yksi tai useampia ohjelmallisesti koodattavia laskentamoottoreita. Kokonaisuutta yhdistää uusi NoC-väyläratkaisu (network on chip). ACAP on erittäin pitkälle ohjelmoitava, ja esimerkiksi I/O-liitännät voidaan toteuttaa Serdes-lohkoisra HBM-muistiväyliin laitteen ja sovelluksen tarpeen mukaan.

Suunnittelijat voivat kehittää toimintoja ja lohkoja ACAP-piireille C/C++-, OpenCL- ja Python-työkaluilla. Piirit voidaan myös ohjelmoida perinteisillä FPGA-työkaluilla RTL-tasolla.

Xilinxin mukaan ACAP-piirit tuovat jopa 20-kertaisen suorituskyvyn esimerkiksi neuraaliverkkolaskentaan verrattuna siihen, että samat algoritmit ajettaisin uusimmilla 16 nanometrin Virtex VU9P -sarjan FPGA-piireillä.

Victor Pengin mukaan Xilinx ei ACAP-julkistuksen jälkeen enää ole vain FPGA-talo. Uutta alustaa on kehitetty neljä vuotta 1500 tuotekehittäjän voimin ja prosessi on maksanut yli miljardi dollaria. Tuloksena on 50 miljardin transistorin uudenlainen ohjelmoitava alusta.

Virtaamamittaus on monissa laitteissa kriittinen mutta usein ongelmallinen toiminto. Perinteiset mekaaniset anturit kuluvat ja jäävät sokeiksi pienille virtausnopeuksille. Ultraäänitekniikkaan perustuvat valmiit moduulit tarjoavat nyt tarkan, huoltovapaan ja helposti integroitavan vaihtoehdon niin kuluttaja- kuin teollisuussovelluksiin.

Virtaamamittaus on monissa laitteissa kriittinen mutta usein ongelmallinen toiminto. Perinteiset mekaaniset anturit kuluvat ja jäävät sokeiksi pienille virtausnopeuksille. Ultraäänitekniikkaan perustuvat valmiit moduulit tarjoavat nyt tarkan, huoltovapaan ja helposti integroitavan vaihtoehdon niin kuluttaja- kuin teollisuussovelluksiin.