Yhä nopeammat ja monimutkaisimmat piirit vaativat paljon ajastuksen suunnittelulta. IDT:n tapaustutkimus osoittaa, miten hankalakin tapaus voidaan ratkaista tiimin yhteistyöllä.

Kirjoittaja Baljit Chandhoke työskentelee Integrated Device Technologyssä ajastinpiirien tuotepäällikkönä. Baljit aloitti  puolijohdealalla piirisuunnittelijalla Infineonilla vuonna 2002. Cypress Semiconductorin sovelluspäällikkönä hän toimi vuosina 2003-2006, jonka jälkeen seurasi viiden vuoden pesti ON Semiconductorilla. IDT:lle hän siirtyi vuonna 2011. Baljit on suorittanut elektroniikkasuunnittelijan tutkinnon Mumbain yliopistossa Intiassa. Lisäksi hänellä on tietoliikennetutkinto Boulderin yliopistosta Coloradosta sekä liiketalouden opintoja Arizonan Staten ja Stanfordin yliopistoissa. puolijohdealalla piirisuunnittelijalla Infineonilla vuonna 2002. Cypress Semiconductorin sovelluspäällikkönä hän toimi vuosina 2003-2006, jonka jälkeen seurasi viiden vuoden pesti ON Semiconductorilla. IDT:lle hän siirtyi vuonna 2011. Baljit on suorittanut elektroniikkasuunnittelijan tutkinnon Mumbain yliopistossa Intiassa. Lisäksi hänellä on tietoliikennetutkinto Boulderin yliopistosta Coloradosta sekä liiketalouden opintoja Arizonan Staten ja Stanfordin yliopistoissa. |

Kun kellotaajuudet kasvavat ja järjestelmistä tulee yhä monimutkaisempia, myös suorituskykyisen vähän tehoa kuluttavan järjestelmän kellopuun rakentamisesta tulee yhä haastavampaa tiukassa tehobudjetissa. Nykyään suunnittelijat kohtaavat usein keskenään ristiriitaisia rajoituksia. Kellojaksojen kutistaminen nopeissa sovelluksissa kuten 10 gigabitin ethernetissä tai optisissa siirtoverkoissa vaativat yhä enemmän signaalin värinältä (jitter) jotta koko järjestelmän suorituskyky säilyisi. Samaan aikaan järjestelmän monimutkaisuuden ja tiheyden lisääntyminen voi tehdä lämmönhallinnasta erittäin hankalaa, kun suunnittelijoiden pitää kutistaa käyttämäänsä levyalaa ja vähentää materiaalikustannuksia. Samoin suunnittelijoiden täytyy toteuttaa suunnittelunsa joustavammin tukeakseen useita ohjelmointitaajuuksia ja lähtöjä, sekä kykyä uudelleen ohjelmoida näitä taajuuksia viime hetken muutosten takia.

Jokin aika sitten IDT:n suunnittelijat kohtasivat monet näitä ongelmista, kun asiakas vaati kellopuusuunnittelua suorituskykyiselle palvelinkoneen verkkosovellukselle. Suunnittelu edellytti, että kellopuu tukee useita taajuuksia useilla lähdöillä. IDT:n tiimille tehtävä oli selvä: piti keksiä ratkaisu, joka integroisi useita erilaisia, eri kellolla operoivia piirisarjoja samalla säilyttäen parhaan mahdollisen pienivärinäisen signaalin, ja pienentäen tehonkulutusta ja piirialaa tiukassa suunnitteluaikataulussa. Tämä artikkeli tarkastelee tuota kehitettyä kelloratkaisua ja esittää, kuinka hyödyntämällä ohjelmoitavien kellosignaaligeneraattorien uusimpia ominaisuuksia tiimi onnistui vastaamaan asiakkaan vaatimuksiin.

Useita haasteita

Yksinkertainen on termi, joka harvemmin liitetään tämän pivän kellopuusuunnitteluun. Tämä tapaus ei ollut poikkeus. Ensiksikin asiakas tarvitsi erittäin suorituskykyisen, pienivärinäisen ratkaisu, joka toimisi pienimmällä mahdollisella teholla. He tarvitsivat ajoitusratkaisu, joka tukisi kahta suorituskykyistä kytkintä. Näissä olisi molemmissa neljä itsenäistä, ohjelmoitavaa taajuutta, jotka piti voida konfiguroida yhdeksi monista differentiaalisista tai yksipäiseksi lähdöksi. Lisäksi he halusivat kompaktin, pitkälle integroidun ratkaisun, joka pienentäisi materiaalikustannuksia ja vaadittua piirikorttialaa, olisi suhteellisen helppo toteuttaa ja veisi tuotteen nopeasti markkinoille.

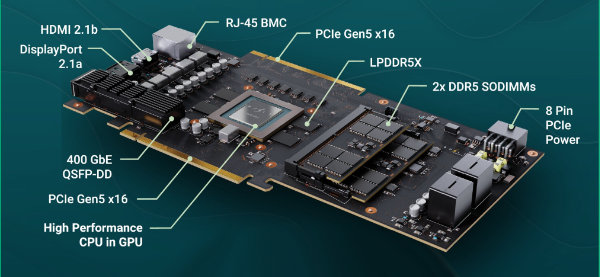

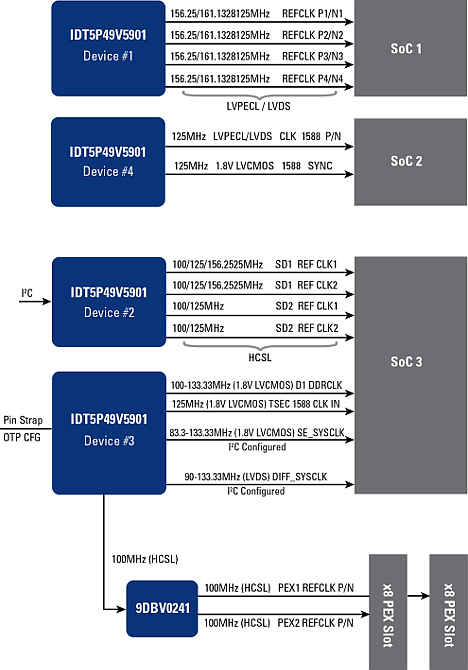

Lopullinen ratkaisu on esitetty alla olevassa lohkokaaviossa. Keskeinen rakennusosa tässä kellopuussa oli IDT:n ohjelmoitava VersaClock 5 - kellogeneraattori (5P49V5901). Usean lähdön ja pienen tehokulutuksen ajoitusratkaisu on suunniteltu tuomaan joustavuutta sovelluksiin, joissa vaaditaan hyvin alhaista värinää, kuten dataliikenteen sovellukset.

Pitkälle integroidussa ohjelmoitavassa kellogeneraattorissa on neljä yleistä parilähtöä, jotka voivat tuottaa neljä erillistä kellosignaalia aina 350 megahertsiin asti erityyppisinä, kuten LCPECL-, LVDS-, HCSL- ja LVCMOS-signaaleina. Taajuudet generoidaan yhdestä referenssikellosta tai kidetulosta. Lähtöjen jakajat voidaan ohjelmoida I2C-liitännän kautta samaan aikaan, kun piiri toimii järjestelmässä. Kentällä tehtäviä päivityksiä varten piirillä on haihtumatonta muistia.

Kuten lohkokaavio alla esittää, yksi IDT5P49V5901-piiri (Device #1) tukee tehokasta 10G-linkin fyysistä osaa (PHY) useilla 10 gigabitin kello- ja datanpalautuspiireillä. Piiri tuottaa neljä referenssikello tiheitä 10G- ja 40G-sovelluksia varten. Sen matala tehonkulutus ja pieni viive maksimoivat datakeskuksen, palvelimen ja kytkimen tehokkuuden. Järjestelmäkytkintä varten 1-piiri tuottaa neljä valittavissa olevaa I2C:n kautta ohjelmoitavaa taajuutta (joko 156,25 tai 161,1328125 megahertsiä), sekä valittavat lähtöliitännät, joita ovat LVPECL tai LVDS.

Toinen IDT5P49V5901-piiri (Device # 4) tukee toista järjestelmäkytkintä, jossa on kaksi ohjelmoitavaa taajuutta: 125 megahertsin lähtö LVPECL- tai LVDS-signaalian ja toinen 125 megahertsin 1,8-volttinen LVCMOS-lähtö. Tämän 10GBASE-T:n fyysinen osa on tehonkulutukseltaan alhainen mutta suorituskykyinen 10G/1G/100M-lähetinvastaanotin, joka on suunniteltu prosessoimaan kaikki 10G-linkin fyysisen tason toiminnot yli sadan metrin kaapelissa. PHY-osaan on lisäksi integroitu RFI-poisto- ja MDI-suodatustekniika, jotta suorituskyky datakeskuksissa säilyisi korkeana ja samalla voidaan kutistaa linkin vaatimaa alaa ja sen kustannuksia. Kytkin tukee useita eri järjestelmäliitäntöjä (full KR, XFI, RXAUI, XAUI ja SGMII) ja yksiporttinen laite sopii erityisen hyvin verkkopalvelimiin sekä LAN-yhteyden toteuttamiseen emolevyillä.

Lisäksi ratkaisussa on kaksi muuta ohjelmoitavaa IDT5P49V5901-kellogeneraattoria, jotka tukevat suorituskykyistä tietoliikenneprosessoria. Tässä moniytimisessa suorittimessa on useita dataliikenne- ja verkkoliitäntöjä. Tässä tapauksessa yksi IDT5P49V5901 (Device #2) tuo neljä ohjelmoitavaa taajuutta (kaksi 100/125 tai 156,25 megahertsin ja kaksi 100- tai 125-megahertsistä HSCL-lähdöillä). Viimeinen kellogeneraattori tuottaa kolme tai neljä taajuutta toteutuksesta riippuen. Tässä sovelluksissa piiri tuottaa kolme tai neljä taajuutta, toteutuksesta riippuen. Tässä tapauksessa kellopiiri tuottaa myös sadan megahertsin HCSL-kanavan 2-lähtöiselle PCIe-puskurille.

Parempi suorituskyky, matalampi tehonkulutus

Ehdotettu ratkaisu vastasi asiakkaan koviin värinävaatimuksiin. Vaihevärinäarvoksi kirjattiin 0,7 pikosekuntia (RMS) koko 12 kilohertsin - 20 megahertsin alueella. Tämä täyttää niin PCI Expressin 1-, 2- ja 3-generaation kuin 1G/10G-ethernetin vaatimukset. Samalla IDT:n ratkaisu pienensi tehonkulutusta (ydintehonkulutus alle 100 mW) ja helpotti piirikortin lämpösuunnittelua. Tämä VersaClock 5:n erittäin pieni tehoarvo auttoi vähentämään kellopuun tehonkulutusta yli 75 prosenttia aiempaan suunnitteluun verrattuna. Uusi suunnittelu pienensi myös piirikortilla tarvittavaa alaa sekä BOM-kustannuksia. Yhdellä piirillä korvattiin useita kiteitä ja oskilaattoripiirejä, mikä pienensi selvästi komponenttien määrää ja kutisti ratkaisun kokoa. Näytepiirien välitön saatavuus ja evaluointikortit lyhensivät puolestaan kehitysaikaa ja mahdollistivat tuotteen nopeamman valmistumisen.

Asiakas piti myös kellopuun joustavuudesta. Yli tusina itsenäistä taajuutta ja valikoima erilaisia yksipäisiä ja differentiaalilähtöjä ohjelmoitavuuden arvo kasvoi. Sen lisäksi, että VersaClock 5 on ohjelmoitavissa I2C-liitännän kautta, piirillä on myös neljä kertaohjelmoitavaa muistipankkia. Tämä avasi ohjemoinnille uusia mahdollisuuksia. Esimerkiksi piirin #1 tukeman kytkimen taajuuden piti olla vaihdettavissa (156,25 MHz ja 161,1328125 MHz). Ohjelmoimalla kertaohjelmoitavat muistit eri taajuuksille asiakas pystyy kytkemään taajuudelta ja lähtösignaalilta toisille käyttämällä valittuja nastoja I2C-liitännän sijaan.

Lisäksi asiakas pystyy käyttämään IDT:n Timing Commander -ohjelmistoa näiden monimutkaisten konfiguraatioiden asettamiseen. Työkalun avulla VersaClock 5:n asetukset voidaan asettaa graafisessa käyttöliittymässä. Työkalun avulla voitiin ohjelmoida neljä lähtöjakajaa tuottamaan neljä itsenäistä lähtötaajuutta tai konfiguroimaan lähtöparit differentiaalisian lähtinä tai kahtena yksipäisenä LVCMOS-signaalilähtönä. Käyttäjä pystyi myös ohjaamaan järjestelmää ohjelmoimaan piirin I2C-liitännän kautta käynnistyksen yhteydessä, mikä ohitti tarvittaessa kertaohjelmoitavaan muistiin tallennetun konfiguroinnin.

Lopuksi

Kuten suunnitteluesimerkki osoittaa, tämän päivän suurta suorituskykyä edellyttävät dataliikenne- ja verkkojärjestelmät vaativat monimutkaisia ajastinratkaisuja. Yksinkertaiset erillispiireihin pohjaavat ratkaisut eivät enää riitä. Yhä useammin suunnittelijat tarvitsevat edistyneitä, pitkälle integroituja kellogeneraattoreita, jotka ovat pitkälle ohjelmoitavissa ja vastaavat silti kiihtyviin suorituskyvyn ja yhä alhaisemman tehonkulutuksen vaatimuksiin.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.