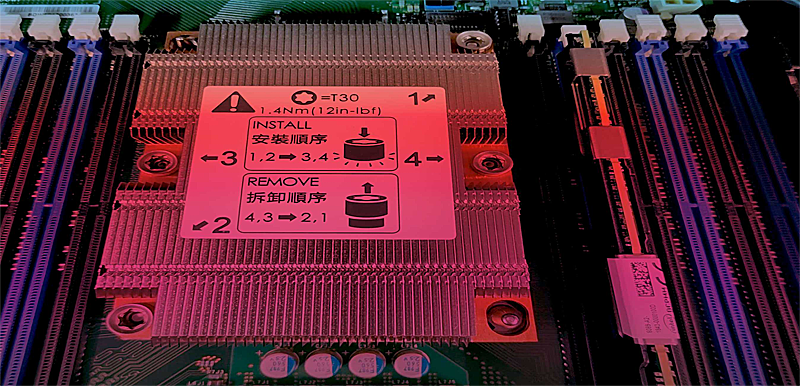

AMD on saavuttanut merkittävän virstanpylvään tuomalla ensimmäisen korkean suorituskyvyn tietojenkäsittelyyn eli HCP-koneisiin tarkoitetun sirun TSMC:n huippumodernille 2 nanometrin N2-prosessille. Uuden sukupolven EPYC-prosessori, koodinimeltään "Venice", on ensimmäinen tuote, joka on tuotu esiin ja validoitu tällä teknologialla.

Yhteistyö TSMC:n kanssa on ollut keskeisessä roolissa AMD:n suunnitelmissa kehittää datakeskusprosessoreitaan. "Venice" on suunniteltu tarjoamaan merkittävästi parempaa suorituskykyä ja energiatehokkuutta, ja sen odotetaan saapuvan markkinoille vuoden 2026 aikana.

Lisäksi AMD ilmoitti onnistuneesta 5. sukupolven EPYC-prosessorien käyttöönotosta TSMC:n uudessa Arizonan tehtaassa, mikä vahvistaa yhtiön sitoutumista Yhdysvaltain valmistukseen ja toimitusketjujen vahvistamiseen.

AMD:n toimitusjohtaja Dr. Lisa Su korosti tiedotteessa pitkäaikaisen TSMC-kumppanuuden merkitystä. - Olemme ylpeitä siitä, että voimme olla TSMC:n N2-prosessin ja Arizonan tehtaan johtava HPC-asiakas. Yhteistyömme vie teknologiarajojen rikkomisen uudelle tasolle.

Kuvassa AMD:n pääjohtaja Lisu Su ja TSMC:n pääjohtaja C.C. Wei.

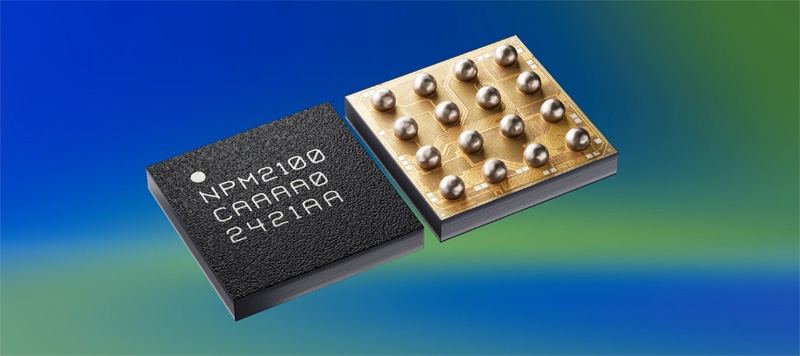

STMicroelectronics on tehnyt merkittävän teknologisen läpimurron julkaisemalla uuden sukupolven älyanturin, joka yhdistää kaksi erillistä kiihtyvyysanturia samaan poikkeuksellisen pieneen (3 x 2,5 mm) koteloon. Tämä on ensimmäinen kerta, kun samassa moduulissa yhdistyy laajalle G-voima-alueelle skaalautuva mittauskyky, sulautettu tekoäly ja erittäin tarkka liikkeentunnistus.

STMicroelectronics on tehnyt merkittävän teknologisen läpimurron julkaisemalla uuden sukupolven älyanturin, joka yhdistää kaksi erillistä kiihtyvyysanturia samaan poikkeuksellisen pieneen (3 x 2,5 mm) koteloon. Tämä on ensimmäinen kerta, kun samassa moduulissa yhdistyy laajalle G-voima-alueelle skaalautuva mittauskyky, sulautettu tekoäly ja erittäin tarkka liikkeentunnistus.

Vaikka monet organisaatiot ovat jo ottaneet käyttöön perinteisiä tekoälyagentteja, tie täysin autonomisiin tekoälyagentteihin voi sisältää haasteita. Tekemällä strategisia investointeja ja omaksumalla metodisen lähestymistavan agenttien skaalaamiseen, sekä niiden erityisten roolien määrittelyyn, teollisuusyritykset voivat päästä loputtomalta tuntuvien kokeilujen yli ja alkaa nauttia tekoälyagenttien hyödyistä todellisessa elämässä, kirjoittaa teollisuuden ohjelmistoja kehittävän IFS:n tekoälyjohtaja Bob De Cuax.

Vaikka monet organisaatiot ovat jo ottaneet käyttöön perinteisiä tekoälyagentteja, tie täysin autonomisiin tekoälyagentteihin voi sisältää haasteita. Tekemällä strategisia investointeja ja omaksumalla metodisen lähestymistavan agenttien skaalaamiseen, sekä niiden erityisten roolien määrittelyyn, teollisuusyritykset voivat päästä loputtomalta tuntuvien kokeilujen yli ja alkaa nauttia tekoälyagenttien hyödyistä todellisessa elämässä, kirjoittaa teollisuuden ohjelmistoja kehittävän IFS:n tekoälyjohtaja Bob De Cuax.

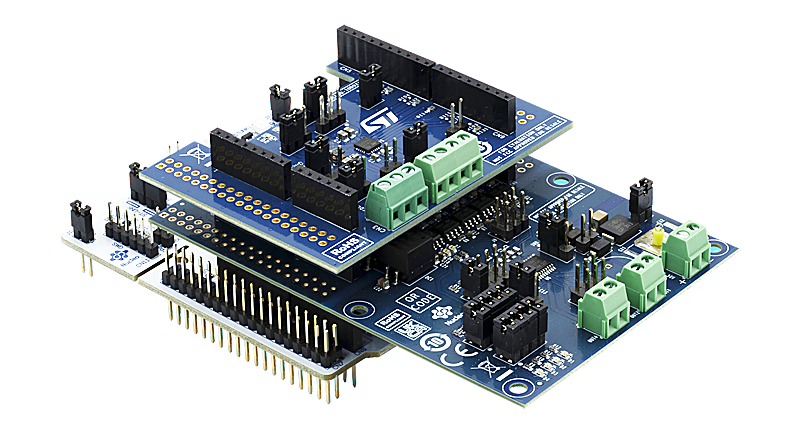

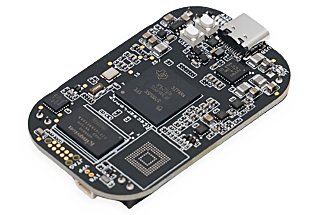

BeagleBoard.orgin tunnettu PocketBeagle-kehittäjäkortti on saanut merkittävän päivityksen uudessa PocketBeagle 2 -versiossa. Uudistuksessa laitteeseen on lisätty neliytiminen suoritin ja ensimmäistä kertaa myös grafiikkaprosessori, mikä avaa entistä laajempia mahdollisuuksia sulautettujen järjestelmien kehittämiseen.

BeagleBoard.orgin tunnettu PocketBeagle-kehittäjäkortti on saanut merkittävän päivityksen uudessa PocketBeagle 2 -versiossa. Uudistuksessa laitteeseen on lisätty neliytiminen suoritin ja ensimmäistä kertaa myös grafiikkaprosessori, mikä avaa entistä laajempia mahdollisuuksia sulautettujen järjestelmien kehittämiseen.