Yhdysvaltalainen puolijohdealan startup Zero ASIC on julkistanut maailman ensimmäisen avoimen standardin mukaisen eFPGA-tuotteen nimeltä Platypus. Tämä julkaisu voi merkitä käännekohtaa koko FPGA-teollisuudelle samalla tavalla kuin RISC-V-arkkitehtuuri on mullistanut CPU-markkinat.

Yhdysvaltalainen puolijohdealan startup Zero ASIC on julkistanut maailman ensimmäisen avoimen standardin mukaisen eFPGA-tuotteen nimeltä Platypus. Tämä julkaisu voi merkitä käännekohtaa koko FPGA-teollisuudelle samalla tavalla kuin RISC-V-arkkitehtuuri on mullistanut CPU-markkinat.

Zero ASIC:n uusi Z1000-gf12lp-piiri on monella tapaa ainutlaatuinrn. Se on sataprosenttisesti avoimeen arkkitehtuuriin perustuva ja kehittäjä saa käyttöönsä täysin avoimen bittivirran. Myös kehitystyökalut ovat 100-prosenttisesti avoimia.

Yrityksen tavoitteena on luoda standardoitu FPGA-ekosysteemi, joka vähentää riippuvuutta yksittäisistä toimittajista, torjuu osien vanhenemista ja helpottaa pitkäikäisten sovellusten, kuten ilmailun ja puolustuksen sovellusten kehitystä.

Yrityksen perustaja Andreas Olofsson on syntyjään ruotsalainen, ja tunnettu puolijohdealan vaikuttaja erityisesti ohjelmoitavan logiikan ja chiplet-arkkitehtuurien alueilla. Olofssonin tausta näkyy vahvasti Zero ASIC:n visiosta demokratisoida piisuunnittelu ja vähentää globaalia riippuvuutta suljetuista teknologioista.

Olofsson haluaa ennen kaikkea demokratisoida FPGA-kehityksen. FPGA-laitteistojen suljetut arkkitehtuurit ja työkalut ovat aiheuttaneet massiivisia ongelmia erityisesti kriittisissä järjestelmissä. Yhdysvaltojen puolustusministeriön on arvioitu menettäneen jopa 70 miljardia dollaria FPGA-komponenttien vanhenemiseen liittyvissä kustannuksissa. Samalla jopa 15 % varaosista arvioidaan olevan väärennettyjä.

Zero ASIC pyrkii muuttamaan tämän tilanteen julkaisemalla avoimen arkkitehtuurin Apache-lisenssillä, mahdollistaen yhteentoimivien toteutusten kehityksen aivan kuten RISC-V International teki avoimen CPU-käskysarjan kanssa.

Zero ASIC:n Platypus eFPGA on jo nyt saatavilla varhaisille asiakkaille, ja yhtiön seuraava työkalu – FPGA Architect – julkaistaan vuoden 2025 toisella neljänneksellä.

Lisätietoja täällä.

Elisa ja Nokia laajentavat 5.5G-verkon eli 5G Advancedin kattavuutta Suomessa ja Virossa, mutta verkon hyödyt jäävät vielä harvojen käyttöön päätelaitteiden puutteen vuoksi. Elisan teknologiajohtaja Sami Komulaisen mukaan uusi verkko on jo käytössä tietyillä alueilla. - Elisan 5.5G kattaa tällä hetkellä osan pääkaupunkiseudusta sekä Tampereen, Turun ja Jyväskylän aluetta, Komulainen sanoo.

Elisa ja Nokia laajentavat 5.5G-verkon eli 5G Advancedin kattavuutta Suomessa ja Virossa, mutta verkon hyödyt jäävät vielä harvojen käyttöön päätelaitteiden puutteen vuoksi. Elisan teknologiajohtaja Sami Komulaisen mukaan uusi verkko on jo käytössä tietyillä alueilla. - Elisan 5.5G kattaa tällä hetkellä osan pääkaupunkiseudusta sekä Tampereen, Turun ja Jyväskylän aluetta, Komulainen sanoo.

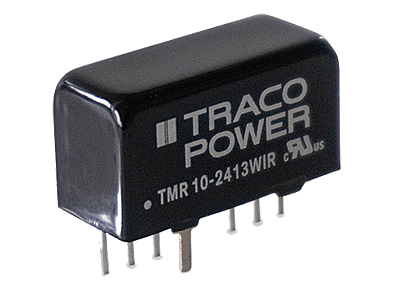

Traco Powerin uusi TMR 10WIR -sarja tarjoaa jopa 10 watin tehon vain sokeripalan kokoisessa SIP-8-metallikotelossa. Poweri on kvalifioitu käyttöön rautateillä. Kompakti DC/DC-muunnin on suunniteltu erityisesti vaativiin liikenne- ja teollisuussovelluksiin, joissa tila on kortilla, mutta laatuvaatimukset korkealla.

Traco Powerin uusi TMR 10WIR -sarja tarjoaa jopa 10 watin tehon vain sokeripalan kokoisessa SIP-8-metallikotelossa. Poweri on kvalifioitu käyttöön rautateillä. Kompakti DC/DC-muunnin on suunniteltu erityisesti vaativiin liikenne- ja teollisuussovelluksiin, joissa tila on kortilla, mutta laatuvaatimukset korkealla.