Uusia arkkitehtuureja radio- ja liitäntäverkoille tarvitaan, koska uudet 5G NR -verkkomääritykset muuttuvat jatkuvasti. Vaikka 5G NR -arkkitehtuuri sisältää uusia taajuuksia ja massiivisia MIMO-antenneja (mMIMO), vastaavan liitäntäverkkoarkkitehtuurin on myös kehityttävä pystyäkseen toteuttamaan 5G:n lupaamat palvelut.

Uusia arkkitehtuureja radio- ja liitäntäverkoille tarvitaan, koska uudet 5G NR -verkkomääritykset muuttuvat jatkuvasti. Vaikka 5G NR -arkkitehtuuri sisältää uusia taajuuksia ja massiivisia MIMO-antenneja (mMIMO), vastaavan liitäntäverkkoarkkitehtuurin on myös kehityttävä pystyäkseen toteuttamaan 5G:n lupaamat palvelut.

|

Artikkelin on kirjoittanut Awanish Verma. Hän toimii pääarkkitehtina Xilinxin langallisten ja langattomien tuotteiden ryhmässä. |

Näihin palveluihin kuuluvat parannettu mobiililaajakaista, erittäin luotettavat matalan viiveen yhteydet ja massiivinen koneiden välinen tietoliikenne. Näiden palvelujen toteuttaminen edellyttää verkon viipalointia sen liitäntäsolmujen eri tasoilla. Pelkästään ohjelmistoilla ei voida vastata kasvaneen datanopeuden ja kutistuvan viiveen vaatimuksiin. Tämä kasvattaa tarvetta kiihdytykselle, joka voidaan parhaiten toteuttaa adaptiivisella ja/tai ohjelmoitavalla laitteistolla. Tässä tarkastelemme 5G-verkkojen kiihdytyksen ensimmäistä tasoa adaptiivisten radiotaajuisten järjestelmäpiirien avulla.

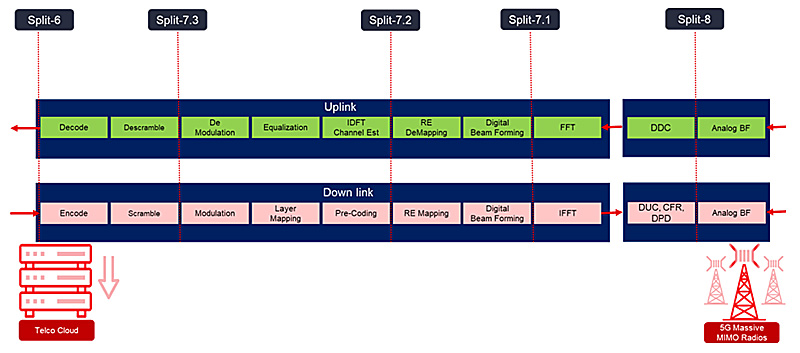

3GPP-standardointiorganisaatiot ovat määrittäneet erilaiset jaetut arkkitehtuurit 5G -radioyksiköiden (RU) ja 5G-tukiasemien välillä, jotta nämä uudet vaatimukset voidaan käsitellä. Ylemmän kerroksen jaot määrittävät toiminnalliset osion keskitetyn yksikön (CU) ja hajautetun yksikön (DU) välillä, kun taas alemman kerroksen jako määrittää toiminnallisen osion radio- (RU) ja DU-yksikön välillä. Alemman kerroksen (RU-DU) jako on kriittisempi ja herkempi ajoituksen ja viiveen suhteen, eikä sitä ole standardoitu.

Kuva 1: Alemman tason jakoon on useita vaihtoehtoisia ratkaisuja.

Vaikka 8-jako on yleisempi perinteisille 4G-LTE-verkoille, 7.2-jako on yleisempi 5G-verkoille. Sille on olemassa useita muunnelmia, joten sitä kutsutaan myös vaihtoehdoksi 7-2x, koska se voi siirtyä vasemmalle tai oikealle, kuten yllä olevasta kuvasta näkyy. Tämä riippuu käyttöönottoskenaarioista. Koska jakamisvaihtoehdot ovat joustavia, eikä DU:n ja RU:n välistä rajapintaa ole määritelty jäykästi rajapintaprotokollien, kaistanleveyden, viiveen ja ajoituksen suhteen, liitännän ja toiminnallisuuden toteuttamiseen sekä RU:ssa että DU:ssa halutaan yleisesti tehdä adaptiivisilla prosessoreilla.

Kaupallisesti saatavilla olevia verkkokortteja (NIC) voidaan käyttää radion ja kantaajuuslaskennan välisen yhteyden (fronthaul) päättämiseen 5G-tukiasemien DU-laitteissa. ASIC-pohjaiset kortit voivat kuitenkin käsitellä vain L2-L3-liikennettä ja ovat riippuvaisia O-RAN-käsittelyn ohjelmistosta. Myös ajoituksen synkronointi ei ole käytettävissä useimmissa yleiskäyttöisissä verkkokorteissa. Koska DU-laitteiden ajoitussynkronointi radiolaitteiden ja viereisten tukiasemien kanssa on tehtävä ankaran tarkasti, niiden on tuettava isäntä-, orja- ja rajakellotoimintoja keskitetystä GPS-kellolähteestä. Toinen tärkeä ajoitustoiminto on kellon pidätyspiiri, joka on toteutettu tukiasemalaitteistoon. Sitä tarvitaan kellon synkronoinnin ylläpitämiseen, jos viitekellosignaali katoaa.

Kun RU:sta tuleva radio IQ-data on käytettävissä prosessointia varten, se on luokiteltava tunnistettavaksi käyttäjä-, ohjaus-, hallinta- ja synkronointitason dataksi sekä uplink- että downlink-suunnassa. Synkronointi- ja hallintatasoprotokollaviestien läpimeno on merkittävästi pienempi kuin U-Plane- ja C-Plane-viesteillä, joten suurimman osan aikaa synkronointi- ja hallintaviestit käsitellään ohjelmistossa sovellusten ollessa käynnissä käyttäjätilassa.

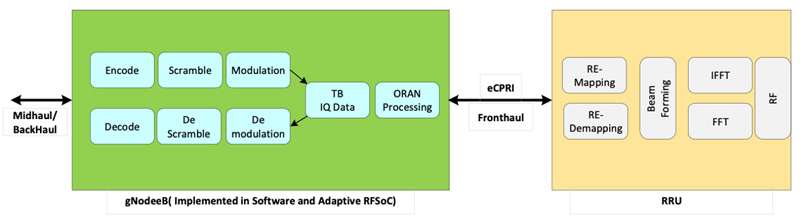

3GPP-vaihtoehto 7-2 jakaa myös selkeän jaon korkean PHY- ja matalan PHY-toiminnon välillä, jossa matalammat fyysisen tason toiminnot, kuten esikoodaus, FFT/IFFT ja resurssielementtien (RE) mappaus/poistotoiminnot toteutetaan joko etäradioyksikössä (RRU) tai radion ja kantataajuusosan verkkosolmussa, jossa kootaan liikenne radioyksiköistä RU:n ja DU:n välillä. Korkean tason fyysiset toiminnot, joihin kuuluvat pääasiassa koodaus/dekoodaus, sekoitus ja modulointi/demodulaatiot suoritetaan DU:ssa.

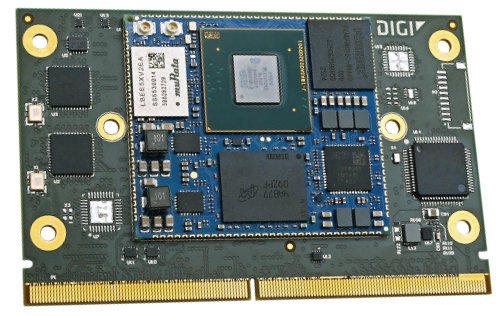

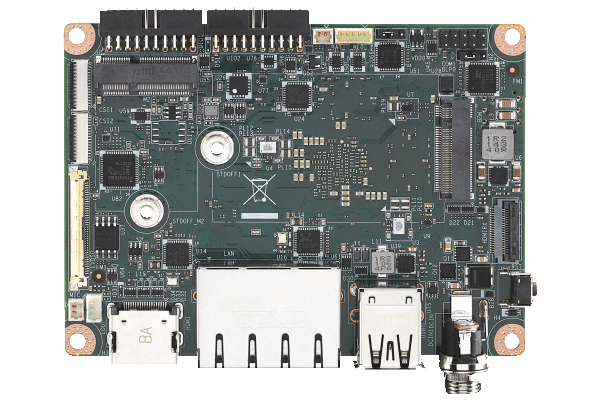

Kuva 2: 5G-option 7-2-jako toteutettuna Xilinxin adaptiivisella RFSoC-piirillä.

GNodeB:n (DU) korkean tason PHY-toiminnot voidaan suorittaa joko kokonaan ohjelmistossa tai ohjelmiston ja mukautettavan laitteiston yhdistelmänä. Ohjelmiston ja laitteiston välinen jako korkean PHY-toiminnon välillä riippuu monista tekijöistä, kuten:

- Ohjelmiston (tai laitteiston) suorituskykyrajat yleiselle suorituskyvylle, ts. ohjelmisto ei saa rajoittaa laitteiston suorituskykyä ja päinvastoin.

- Latenssikysymykset: Koska 5G-määritykset asettavat vahvan latenssivaatimuksen eri palveluluokille, jaon ei pitäisi vaikuttaa latenssiin negatiivisesti.

- Yhteensopivuus alan standardien ohjelmistorajapintojen kanssa: Joillakin korkean tason PHY-toiminnoilla on vakiomääritys käyttäjätilan rajapinnasta, joten kaikkien laitteistototeutusten tulee säilyttää yhteensopivuus vakiorajapintojen kanssa saumattoman siirtymisen varmistamiseksi.

Yllä oleva kuvaus esittää toiminnot, joita tarvitaan Xilinxin kaltaisten yritysten ohjelmoitaville laitteistopohjaisille kiihdyttimille. Ihanteellinen kiihdytinarkkitehtuuri saattaa 5G:ssä vaatia sen, että korkean tason fyysiset toiminnot toteutetaan laitetasolla, mikä mahdollistaa parhaan suorituskyvyn ja pienimmän viiveen samalla kun skaalataan useiden mMIMO-pohjaisten RRU-kokoonpanojen välillä. Kehittyneiden 5G- ja O-RAN-standardien ja -toiminnallisuuksien myötä Xilinx on aloittanut O-RAN-prosessoinnin ja koodauksen/dekoodauksen toteutuksen rinnalla (lookaside) ohjelmoitavissa kiihdytinkorteissa. Kanavakoodaus on yksi kerroksen 1 korkean tason fyysisistä toiminnoista, joka soveltuu parhaiten adaptiiviselle laitteistolla (ASOC, adaptable SoC) laskentaintensiivisen luonteensa vuoksi. Se voidaan myös yhdistää HARQ-toimintoihin (hybrid automatic repeat request) suorituskyvyn edelleen parantamiseksi ja viiveen pienentämiseksi.

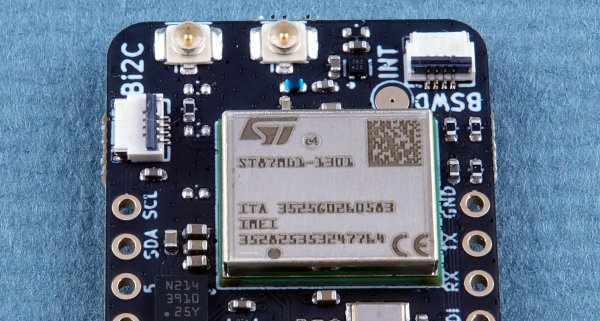

5G:n L1-kerroksen korkean tason fyysisiä toimintoja voidaan nopeuttaa mukautettavilla ja ohjelmoitavilla Xilinx T-sarjan kiihdytyskorteilla (Telco Accelerator Cards). Näillä korteilla on adaptiivinen RFSoC-piiri, joka kovettaa eli vie laitetasolla ohjelmistopohjaiset SD-FEC-virheenkorjauslohkot (SD-FEC, forward error correction) ja toteuttaa myös HARQ-toiminnallisuuden ja sisäisen DRAM-muistin paremman ja skaalautuvamman suorituskyvyn saavuttamiseksi.