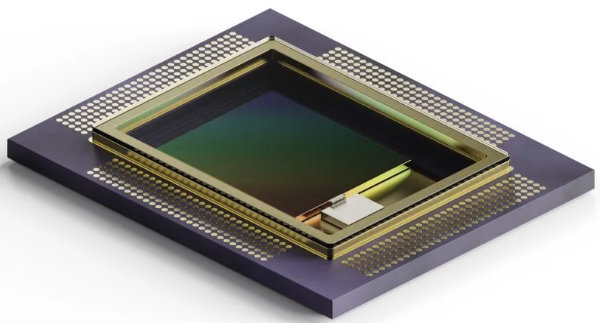

Tampereen yliopistosta ja seitsemästä yrityksestä koostuva SoC Hub -konsortio on suunnitellut valmiiksi toisen järjestelmäpiirinsä, ja se on lähetetty tuotantoon. Valmistuksesta vastaa maailman suurin mikropiirien valmistaja TSMC, ja valmiit piirit saapuvat Suomeen helmikuussa 2023.

Business Finlandin rahoittamassa projektissa kehitetään yhteensä kolme järjestelmäpiiriä vuoden 2023 loppuun mennessä. SoC Hubin ensimmäinen järjestelmäpiiri, Ballast, saatiin valmiiksi loppuvuodesta 2021. Piirit saapuivat valmistuksesta kesäkuussa 2022, ja sen jälkeen toteutettiin onnistuneesti piirin herättäminen eli wake-up. Suurin osa piirin tärkeimmistä toiminnoista saatiin käyttöön ennätysnopeasti yhden päivän aikana.

- Projektille elintärkeät toimintaedellytykset kuten infrastruktuuri ja sopimusympäristö saatiin kuntoon jo ensimmäisen piirin kehityksen aikana, ja sen ansiosta toisen Tackle-järjestelmäpiirin kehitys pystyttiin aloittamaan nopeasti heti projektin ensimmäisen vaiheen jälkeen, kertoo tietotekniikan professori Timo Hämäläinen Tampereen yliopistosta.

Ballastin menestyksekkään toteutuksen ja tavoitteet ylittäneiden ominaisuuksien ansiosta projektipartnerit pystyivät toisen piirin kehitystyössä keskittymään uusien IP-lohkojen kehitykseen. Projektivaiheiden keskinäisen riippuvuuden välttämiseksi Tackle-piirin kohdalla luotiin kokonaan uusi SoC-alusta ja kehitettiin liitettävyyttä. Ohjelmoitava DMA-kontrolleri, LP-DDR2-muistikontrolleri ja High Speed Serdes -tietoyhteys suunniteltiin, verifiointiin ja valmistetaan osana uutta piiriä.

Tacklen kehittämisessä sovellettu ketterä projektimenetelmä mahdollisti Tackle-piirin valmistumisen aikataulussa. RTL-suunnittelussa ja laitteistonläheisessä ohjelmistokehityksessä automaatiota lisättiin käyttämällä ja kehittämällä avoimeen lähdekoodiin perustuvaa Kactus2 IP-XACT-työkalua, joka on Tampereen yliopiston tutkijoiden kehittämä.

Tackle on pinta-alaltaan 4 neliömillimetriä. Piirin valmistuksessa käytetään TSMC:n 22 nanometrin Ultra Low Leakage -puolijohdeteknologiaa, ja se paketoidaan 88-pinniseen QFN-koteloon. Nyt kehitetyt uudet IP-lohkot ovat olennaisia projektin kolmannelle Headsail-piirille, jossa keskitytään matalan tehon suurteholaskentaan.

Seuraavan piirin suunnittelu on jo aloitettu, ja se lähetetään tuotantoon ensi syksynä.

Kuva: Jonne Renvall / Tampereen yliopisto