Seuraavan sukupolven alustat vaativat yhä enemmän innovatiivisia ratkaisuja, jotka kasvattavat suorituskykyä, alentavat tehonkulutusta ja tekevät FPGA-toteutuksista fyysisesti pienempiä. 3D-järjestelmäpiireissä yksi parhaimpia keinoja on Intelin EMIB-liitäntä.

| Artikkelin kirjoittaja Manish Deo toimii nykyisin Intelin omistaman Alteran vanhempana tuotemarkkinoinnin päällikkönä. Hän tuli Alteran palvelukseen vuoden 2006 alussa tuotesuunnitteluun. Suunnittelupäällikkönä Manish toimi vuosina 2008-2012, jonka jälkeen hänen nimitettiin nykyiseen tehtäväänsä. Hänellä on elektroniikkainsinöörin tutkinto Nagpurin yliopistosta Intiasta ja vastaava tutkinto Toledon yliopistosta Yhdysvalloista. |

Seuraavan sukupolven alustojen täytyy kehittyä nopeasti, jotta ne pysyvät nousevien trendien kehityksessä mukana. Tällaisia ovat datakeskus, esineiden internet eli IoT, 400 gigabitin – terabitin verkot, optiset verkot, 5G-mobiilitekniikka, 8K-video ja monet muut. Liitettävyyden ja prosessointitehon kasvu vaikuttaa erityisesti puolijohdealueelle tehokkaampia järjestelmiä ja niihin liittyviä palveluja varten kehitettyihin komponentteihin. Tämän kehityksen lähempi tarkastelu paljastaa mielenkiintoisia trendejä.

Esimerkiksi seuraavan polven datakeskusten työkuormat vaativat yhä suurempaa laskennallista suorituskykyä, joustavuutta ja energiatehokkuutta. Näihin ei tämän päivän yleispalvelimilla ylletä. Lisäksi datakeskuslaitteisto pitää virtualisoida ja toteuttaa palvelunsa kaupallisilla palvelimilla, jotta järjestelmän monimutkaisuus vähenisi ja liiketoiminnasta tulisi ketterämpää ja skaalautuvampaa. Palvelinten suorityskyky on kuitenkin itse asiassa hidastunut, mikä johtuu pääosin tehorajoituksista. Datakeskusratkaisujen suunnittelu spesifejä tehtäviä varten lisää tehokkuutta, mutta rajoittaa samalla ratkaisun yhtenäisyyttä ja joustavuutta. Joustavuus taasen on erityisen tärkeä ominaisuus, kun datakeskuspalvelut kehittyvät nopeasti ja vaativat näin adaptoituvaa laitteistoa.

IoT tuo samanlaisia haasteita. IoT:n ennustetaan kasvavan dramaattisesti ja tuovan markkinoille miljardeja älykkäitä esineitä lähivuosina. Nämä älykkäät esineet tai objektit ovat kaikki yhteydessä verkkoon ja kommunikoivat keskenään tai pilveen tai datakeskukseen. Laitteiston pitää määritellä mikä data pitää prosessoida ja mikä data pitää sivuuttaa, ja tämän pitää tapahtua reaaliajassa. Siksi IoT edellyttää pitkälle verkottunutta, joustavaa, tehokasta, suuren kaistanleveyden laitteistoa, joka mahdollistaa näkemyksen datakeskuksesta verkon reunalle. Tämä vaatimus haastaa palveluntarjoajat, datakeskukset, pilvipalvelut ja tallennusjärjestelmät vastaamaan alati kasvavaan internetliikenteeseen.

Seuraavan polven alustoja luonnehti yksi yhteinen teema: tarve kasvattaa kaistanleveyttä ja toiminnallisuutta samalla, kun tehonkulutusta lasketaan ja laitteiden kokoa pienennetään. Yksinkertaisesti sanottuna näitä seuraavan polven alustoja varten rakennettujen laitteiden täytyy samanaikaisesti kyetä tekemään enemmän, olla nopeampia, viedä vähemmän tilaa piirikortilta ja kuluttamaan vähemmän tehoa. Tämä vaatii innovatiivisia ratkaisuja koko puolijohde-ekosysteemissä.

Tämän takia seuraavan polven alustoja suunnittelevien järjestelmäarkkitehtien täytyy löytää ratkaisut suuremman kaistanleveyden, pienemmän tehonkulutuksen ja pienemmän piialan vaatimuksiin. Lisäksi on aina tarve lisätä laitteiden toiminnallisuutta ja joustavuutta.

Historiallisesti järjestelmäarkkitehdit ovat vastanneet näihin vaatimuksiin pakkaamalla yhä enemmän erilliskomponentteja standardipiirilevylle yrittäen tuottaa maksimaalisen toiminnallisuuden ja suorituskyvyn ja samalla pitää tehobudjetti kurissa. Tämä lähestymistapa on tulossa loogisen tiensä päähän ja sillä on yhä suurempia vaikeuksia vastata kasvaviin vaatimuksiin. Suurimpia haasteita ovat:

- piirien välistä kaistanleveyttä rajoittaa piirikortin sallima liitäntätiheys

- järjestelmän tehonkulutus kasvaa liiaan suureksi, koska komponenttien välille pitää piirilevylle vetää liian pitkiä johtimia

- ratkaisun fyysinen koko kasvaa liian suureksi, koska haluttu toiminnallisuus kasvattaa tarvittavien erilliskomponenttien määrää liiaksi

Järjestelmäarkkitehdit ovat yrittäneet ohittaa nämä rajoitukset tutkimalla joidenkin komponenttien monoliittistä (eli yksisiruista) integraatiota. Tämä integrointi kuitenkin johtaa toisenlaiseen ongelmaan: IP-lohkojen kypsyyteen. Eri IP-lohkot kypsyvät eri prosessisukupolvissa ja tämän takia ne ovat käytettävissä eri aikoina. Siksi ei ole mahdollista integroida kaikkea haluttua toiminnallisuutta tai IP-lohkoja monoliittisina piireinä. Jos valmistaja kehittää esimerkiksi 14 nanometrin logiikkasirua ja haluaa integroida piirille DRAM-muistia, ainoa mahdollisuus on käyttää 40 nanometrin tai sitä vanhemmassa prosessissa valmistettua DRAM-piiriä. Tämä rajoitus estää yhden monoliittisen piirin käyttämisen.

Toinen iso haaste on tarve tuottaa maksimaalinen huippunopea liitäntä laitteiden välille. Monet protokollastandardit kehittyvät edelleen ja tarvittavat datanopeudet ja modulointitekniikat vaihtelevat järjestelmästä toiseen. Siksi on tärkeää määritellä innovatiivinen ratkaisu, jossa voidaan hyödyntää nopeasti nousevia tekniikoita ja IP-lohkoja.

Seuraavan polven järjestelmien nostamat haasteet ovat alkaneet määritellä mahdollisten ratkaisujen joukkoa. Perinteiset ratkaisut eivät taivu tulevaisuuden vaatimuksiin: suurempaan kaistanleveyteen, matalampaan tehonkulutukseen, pienempään fyysiseen kokoon ja lisääntyvään toiminnallisuuteen ja joustavuuteen. Haaste on kehittää innovatiivinen, kaupallisesti kestävä ja skaalautuva ratkaisu, joka vastaa näihin vaatimuksiin.

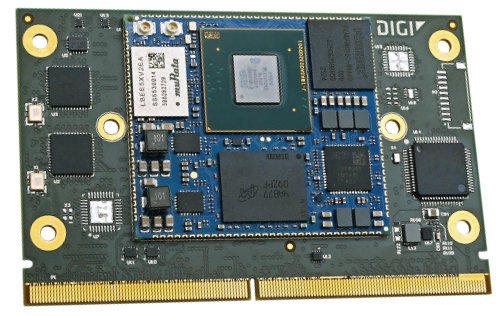

Altera on esitellyt heterogeenisen 3D-järjestelmäkotelon SiP-tekniikan (system-in-package), jonka uskotaan vastaavaan kaikkiin näihin yllämainittuihin vaatimuksiin. Integraatio kotelon sisälle on skaalautuva ja hyvin suoraviivainen valmistaa.

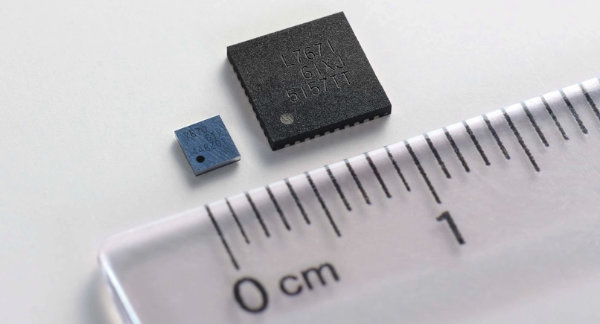

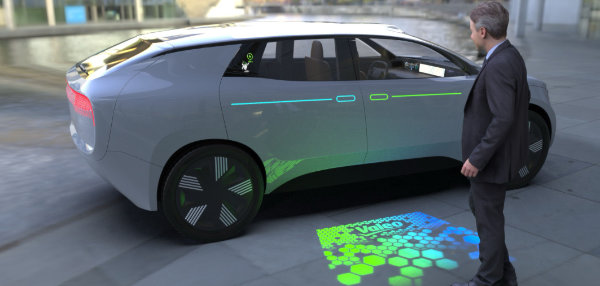

Heterogeeninen 3D SiP -tekniikka mahdollistaa sen, että erilaisia komponentteja integroidaan FPGA-piirin rinnalle yhteen koteloon, jotta uusiin järjestelmävaatimuksiin vastataan. Tämän ansiosta kestäviä ratkaisuja saadaan tuotettua nopeammin kuin aiemmin (ks. kuva 1). Tämä lähestymistapa mahdollistaa hyvin erilaisten komponenttien liittämisen samaan koteloon, kuten analogiapiirien, muistin, ASIC-piirien, prosessorin ja monia muita.

Kuva 1. FPGA-pohjainen heterogeeninen integrointi kotelon sisään.

Lähestymistapa on ainutlaatuinen FPGA-alalla, sillä siinä käytetään yhtä monoliittistä FPGA-ydinmatriisia (jossa on jopa 5,5 miljoonaa logiikkaelementtiä) ja sen ympärille integdoisaan useita piisiruja. Monoliittinen FPGA-piiri tuottaa suorityskyvyn ja varmistaa sen, että data voidaan prosessoida suurimmalla mahdollisella nopeudella ilman, että törmätään reititysongelmiin tai että suorituskyky kärsisi.

Tämän kaiken mahdollistaa Intelin patentoima EMIB-väylätekniikka (Embedded Multi-die Interconnect Bridge). Intel suunnitteli EMIB-väylän ratkaisuihin, jotka vaativat äärimäisen edistynyttä kotelointi- ja testauskykyä. EMIB tuottaa ultratiheän liitännän samassa kotelossa olevien piisirujen välille. Se mahdollistaa myös kotelon sisällä toiminnallisuuden, joka aiemmin oli liian monimutkainen tai kallis vaihtoehtoisilla kotelointegroinnin tekniikoilla toteutettavaksi.

EMIB-teknologia mahdollistaa yksinkertaisemman tuotantoprosessin, paremman suorituskyvyn, kohentuneen signaalineheyden sekä monimutkaisuuden vähemämisen.

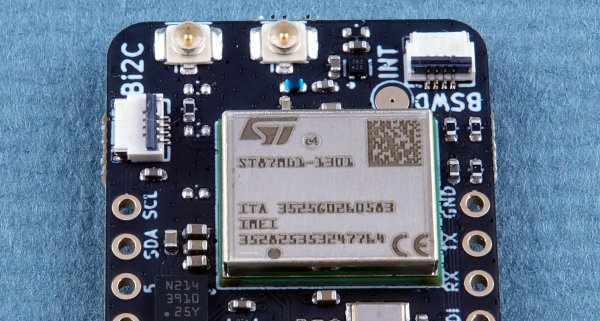

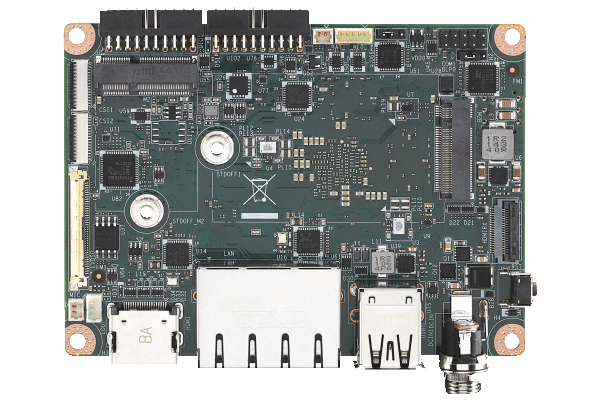

EMIB on pieni piisiru, joka on sulautettu allaolevaan piirialustaan tuoden ultratiheän liitännän sirujen välille. EMIB-rakenne ei sisällä läpivientejä (vias), mikä yksinkertaistaa valmistusprosessori merkittävästi samalla kun signaalin ja sähkölinjan ominaisuuden paranevat. Tärkeää on sekin, etteivät EMIB-liitännän fyysiset mitata rajoita integroitavien sirujen määrää. Vaihtoehtoiset ratkaisut sen sijaan kääntävät suurta piikerrosta, joka asettuu kotelon alustan päälle ja pidentää koko integroitavan sirun pituutta. Tämä välikerros tekee ratkaisusta kalliimman ja altistaa sen erilaisille ongelmille, kuten vääntymiselle. Vaihtoehtoiset menetelmät vaativat myös suuren määrän mikroläpivientejä vaativia mikronystyjä, mitkä heikentävät saantoa ja monimutkaistavat valmistusta. Lisäksi integroitavien sirujen määrä on rajoitettu, mikä vaikuttaa skaalattavuuteen (kuva 2).

Kuva 2. EMIB-toteutus (kuvassa ylhäällä) vaihtoehtoisiin toteutuksiin verrattuna.