AMD on esitellyn uuden sirun edullisten FPGA-piiriensä valikoimaan. Spartan Ultrascale+ on samalla viimeinen edullisten ohjelmoitavien piirien perhe, joka siirtyy 16 nanometrin prosessiin. Uutuus on suunnattu ennen kaikkea liitäntäpiiri, jolta löytyy jopa 572 I/O-linjaa.

AMD on esitellyn uuden sirun edullisten FPGA-piiriensä valikoimaan. Spartan Ultrascale+ on samalla viimeinen edullisten ohjelmoitavien piirien perhe, joka siirtyy 16 nanometrin prosessiin. Uutuus on suunnattu ennen kaikkea liitäntäpiiri, jolta löytyy jopa 572 I/O-linjaa.

Edelliset Spartan-piirit valmistettiin 28 nanometrin prosessissa. Nyt uusi perhe siirtyy 16 nanometrin FinFET-prosessiin, joka on jo kypsä ja testattu toimivaksi lukuisissa AMD:n piireissä. Prosessin myötä Spartanin tehonkulutus pienenee jopa 30 prosenttia, jos verrataan samaan logiikka- ja I/O-resurssimäärään vanhassa prosessissa.

AMD:llä on kolme ”kustannustehokkaiksi” luokiteltua FPGA-perhettä. Artix sisältää eniten logiikkaa ja Zync-piireillä mukaan on integroitu Arm-prosessoreja. Tässä seurassa Spartan sopii ennen kaikkea sovelluksiin, joissa tarvitaan eniten liitäntöjä. Tuotemarkkinoinnista vastaava Rob Bauer muistutti, että Spartan ei ole tyypillisesti laitteen sydän vaan se logiikka, joka sitoo eri osat yhteen.

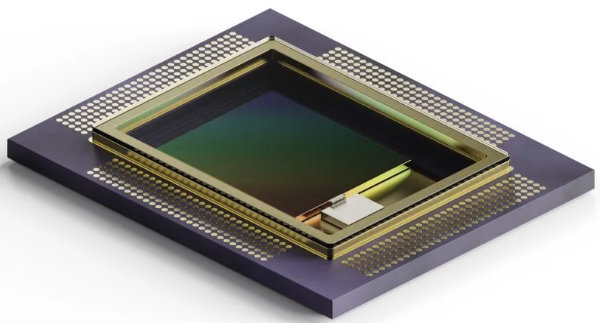

On uudella Spartanilla toki logiikkaresurssejakin, skaala yltää 11 tuhannesta logiikkasolusta aina 218 tuhanteen. Pienimmät versiot ovat kooltaan 10 x 10 millin kotelossa, suurimmatkin vain 23 x 23 -millisiä. Ylemmän pään siruilla on lisätty kaksi kovakoodattua DDR5- ja PCIe-ohjainta.

- Muistiohjain vie FPGA-piirillä noin 30 tuhatta logiikkasolua, joten kovakoodattuna nämä säästävät logiikkaresursseja muihin toimintoihin, Bauer muistutti.

Spartan Ultrascale +:lle on tarjolle yli sata IP-lohkoa. Niille saa esimerkiksi NIST:n sertifioimat, kvanttikoneiden hyökkäykset kestävät PQC-salausalgoritmit. Samalla koko suunnitteluvuo on viety Vivadoon eli koko suunnitteluprosessi onnistuu yksillä työkaluilla. Spartanille Vivado on vielä ilmainen.

Spartan UltraScale+ FPGA -perheen näytepiirit ja evaluointikortit tulevat tarjolle vuoden 2025 ensimmäisellä puoliskolla. Dokumentaatio piireistä löytyy AMD:n sivuilta jo nyt. Lisätietoja täällä.