Pian Intelin omistukseen siirtyvä Altera on esitellyt uuden lippulaivapiirinsä, peräti 5,5 miljoonan logiikkaelementin Stratix 10 -piirin. Siinä ohjelmoitavan matriisin eli varsinaisen FPGA-osion nopeus kasvaa paitsi Intelin prosessin, myös nerokkaan uuden arkkitehtuurin ansiosta.

Alteran markkinointijohtaja Chris Baloughin mukaan FPGA-piirien suorituskykyä on perinteisesti kasvatettu lähinnä Mooren lain voimalla: tiheämpi prosessi tuo nopeammat signaalit ja pienemmän tehonkulutuksen.

Piirien koon jatkuva kasvu on kuitenkin tuonut valmistajille ongelmia, sillä reititys viivästyttää signaalien kulkua jättimäisillä siruilla. Tähän on vastattu aiemmin lähinnä leventämällä väyliä eli lisäämällä johdotusta logiikkaan.

Stratix 10 -piireillä Altera on esitellyt uuden arkkitehtuurin, joka yrittää ratkaista ongelman uudella tavalla. Sen sijaan, että dataväylää levennetään, tehdään signaalipolusta nopeampi. Tätä arkkitehtuuria Altera kutsuu nimellä Hyperflex.

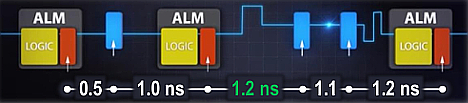

Idea on yksinkertainen. Datapolkua FPGA-matriisin sisällä liukuhihnotetaan. Logiikkayksikköjen välille lisätään uusia rekisterejä, ns. hyperrekisterejä, joiden ansiosta signaalipolkujen pisin rekisterien välinen viive lyhenee merkittävästi. Tämän ansiosta matriisin kellotaajuutta voidaan nostaa ylemmäs.

Alteran esimerkin mukaan viive kahden logiikkayksikön välillä on 3,5 nanosekuntia. Tämän myötä signaalin kellotaajuus voi olla 286 megahertsiä. Kun polulle lisätään rekisterejä, pisin viive lyhenee 1,2 nanosekuntiin ja kellotaajuus kasvaa 833 megahertsiin. Alteran mukaan tällainen yli kaksinkertainen kellotaajuuden kasvattaminen on Hyperflex-arkkitehtuurissa säännönmukaista.

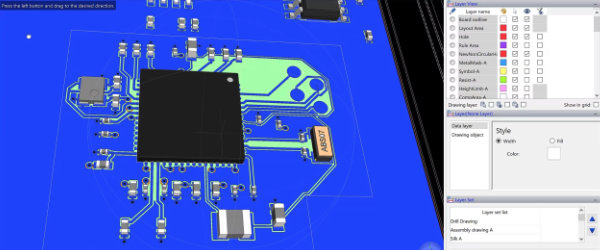

Suunnittelijan kannalta hyvä asia on se, että piirien reititys ei muutu. Quartus II -työkalut tuottavat lisärekisterit automaattisesti sinne, missä niitä tarvitaan ja mihin niitä mahtuu. Ja tilaa FPGA-osiossa on, sillä Hyperflex-rekistereitä sopii logiikkayksikköjen sekaan 10-kertainen määrä enemmän kuin parinteisiä rekistereitä.

Nopeusetua voi käyttää monella tapaa. Jos tarvitaan vain tiettyä suorituskykyä, voidaan vaikkapa 1024-bittinen dataväylä ohentaa 512 bittiin ja saada sama laskentateho aikaa puolta pienemmällä piirillä. Vähemmän piitä tarkoittaa suoraan alempaa hintaa.