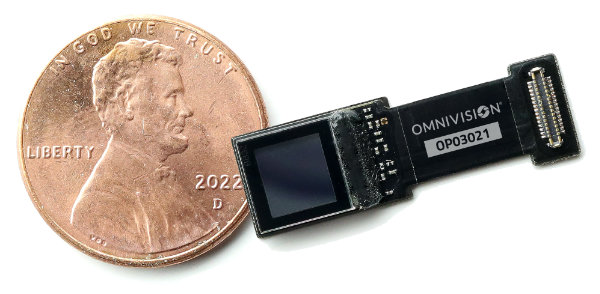

Xilinx ilmoittaa tuovansa ensi vuonna uuden Ultrascale-arkkitehtuurinsa myös Virtex- ja Kintex-piireihinsä. 20 nanometrin prosessissa valmistettavien uutuuksien joukossa on myös seuraavan polven Virtex-lippulaivapiiri. Vu440-sirulla ohjelmoitavia logiikkasoluja on peräti 4,4 miljoonaa.

Xilinxin uutinen tulee vain viikkoa sen jälkeen, kun pahin kilpailija Altera esitteli omien 20 nanometrin sirujensa työkalut. Xilinxin mukaan se on ainakin kaksi vuotta arkkivihollistaan edellä. Uusi VU440-piiri tuo enemmän suorituskykyä kuin mikään Alteran siru seuraavassa eli 14 nanometrin prosessissa.

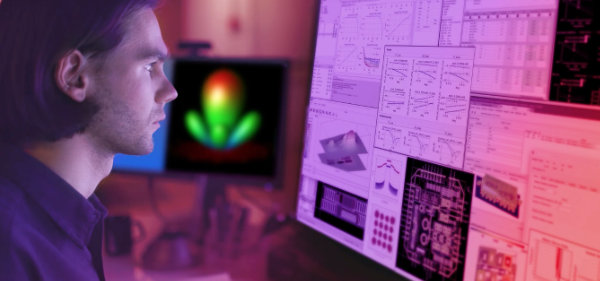

Ultrascale on paljon enemmän kuin aiempaa tiheämpi viivanleveys. 3D-rakenne ja siitä kaiken suorituskyvyn irti ottaminen on vaatinut aivan uuden suunnittelumetodologian kehittämisen. Se kiteytyy uusissa Vivado-työkaluissa.

Xilinsin mukaan Vivadon kehittäminen kesti neljä vuotta ja vaati tuhannen miestyövuoden panostuksen. Projektina kyse on suurin yksittäinen työkalujen kehityshanke koko puolijohdealalla, yritys uskoo.

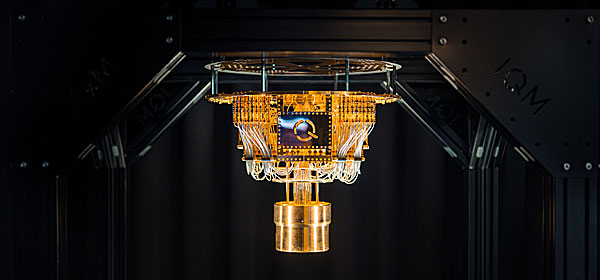

Ultrascale-arkkitehtuuri ratkaisee ennen kaikkea suurimman tiheiden piirien suunnitteluongelmat eli liitännät. 3D-piireissä hyödynnetään uutta SSI-tekniikkaa (Stacked Silicon Interconnect), jonka avulla kaiken ohjelmoitavan logiikan elinikä pitenee, vaikka Mooren lain loppu puolijohteissa jo häämöttääkin. 3d-pinoamisen avulla suurimpien piirien kapasiteetti kasvaa kaksinkertaiseksi aina uuden prosessisukupolven myötä.

Xilinx lupaa Virtex VU 440 -piirien ensimmäisiä näytteitä tarjolle noin vuoden kuluttua. Ultrascale-arkkitehtuuri tähtää seuraavaksi TSMC:n 16 nanometrin FINFET-prosessiin, jota silmällä pitäen arkkitehtuuri on alun perin kehitettykin.

Xilinxilla on TSMC:n kanssa käynissä 16 nanometrin valmistusta varten tähtäävä FinFats-hanke, jossa ensimmäisten testisirujen pitäisi valmistua vielä kuluvan vuoden aikana. Hankkeen edistymisestä ei kuitenkaan ole kovin paljon tähän asti kerrottu.