Suurten järjestelmäpiirien toiminnallisuuden tarkistaminen eli verifiointi on kallista ja aikaa vievää. Mentor Graphics haluaa nopeuttaa verifiointi uudella EVP-alustallaan (Enterprise Verification Platform), jossa yhdistetään verifointityökalut tehokkaan laitetason emulointiin ja virheentarkistukseen.

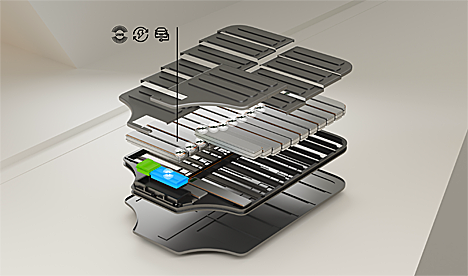

Käytännössä samalle alustalle yhdistetään verifioinnin Questa-työkalut, Veloce OS 3 -emulaattori sekä debuggauksen Visualizer-ympäristön. Mentorin mukaan tänä parantaa verifioinnin tehokkuuden 400-10000-kertaiseksi nykymetodologiaan verrattuna.

Mentorin verifiointidivisioonaa johtavan John Lenyon mukaan uuden alustan visiona on irrottaa verifiointiprosessi itse verifioinnin työkaluista tai laitteistosta. - EVP-alusta yhdistää simuloinnin emuloinnin nopeuteen, Lenyo kehuu.

Osa uutta visiota on viedä emulointi pois projektipohjaisesta ajattelusta. Sen sijaan emuloinnista tulee uudessa mallissa datakeskuspohjainen globaali resurssi. Samalla päästään eroon vanhasta ICE-emuloinnin (I-Circuit Emulation) kaapeloinnista ja muista fyysisistä laitteista, ja ne korvataan virtuaalisilla laitteilla ja resursseilla.

Veloce OS3 -emulaattoreiden VirtuaLAB-oheislaitteet voidaan konfiguroida niin, että emulointikapasiteettia voidaan jakaa eri projektien kesken. VirtuaLAB-toimintoa ajetaan standardeilla palvelinkoneilla.

Emulointiresurssien jakoa hallitaan OS3 Enterprise Server -palvelinohjelmistolla, joka osaa esimerkiksi sijoittaa kunkin emulointiprojektin sopivimpaan palvelinkeskukseen. Ohjelmisto myös priorisoi projekteja, joten kiireellisimmät projektit saavat laskentaresurssit ensiksi käyttöönsä.

Mentorin mukaan EVP-alustan komponentit tulevat yleiseen jakeluun toisen neljänneksen loppuun mennessä.

Analog Devices päätti jokin aika sitten lopettaa yhteistyön englantilaisen jakelijan Anglia Componentsin kanssa. Tässä ei ole sinänsä mitään ihmeellistä, mutta Anglia suivaantui tästä niin paljon, että tuli julkisuuteen asian kanssa. Toimitusjohtaja Steve Rawlinsin mukaan ADI:n päätös rajoittaa asiakkaiden valinnanvaraa.

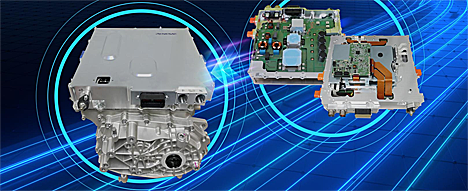

Analog Devices päätti jokin aika sitten lopettaa yhteistyön englantilaisen jakelijan Anglia Componentsin kanssa. Tässä ei ole sinänsä mitään ihmeellistä, mutta Anglia suivaantui tästä niin paljon, että tuli julkisuuteen asian kanssa. Toimitusjohtaja Steve Rawlinsin mukaan ADI:n päätös rajoittaa asiakkaiden valinnanvaraa. Murata on julkistanut maailman ensimmäisen yhteysmoduulin, joka tukee uutta SGP.32 Remote SIM Provisioning (RSP) -spesifikaatiota osana integroitua SIM-teknologiaa (iSIM). Tämä uusi ratkaisu pohjautuu Muratan innovatiiviseen Type 2GD Cat.M1/NB-IoT -yhteysmoduuliin, joka tukee ETSI/3GPP Release 17 -standardia, sekä Giesecke+Devrientin (G+D) korkeasti suojattuun SGP.32-yhteensopivaan SIM-käyttöjärjestelmään.

Murata on julkistanut maailman ensimmäisen yhteysmoduulin, joka tukee uutta SGP.32 Remote SIM Provisioning (RSP) -spesifikaatiota osana integroitua SIM-teknologiaa (iSIM). Tämä uusi ratkaisu pohjautuu Muratan innovatiiviseen Type 2GD Cat.M1/NB-IoT -yhteysmoduuliin, joka tukee ETSI/3GPP Release 17 -standardia, sekä Giesecke+Devrientin (G+D) korkeasti suojattuun SGP.32-yhteensopivaan SIM-käyttöjärjestelmään.