Sveitsiläiset ja japanilaiset tutkijat ovat viisi vuotta yrittäneet kutistaa RISC-V-arkkitehtuuriin perustuvan piirin tehonkulutusta. Nyt uutisoitu työ on tuottanut hedelmää, sillä uusin versio leikkaa piirin tehonkulutuksen valmiustilassa yhteen pikowattiin bittiä kohti.

Asialla ovat CSEM-tutkimuslaitoksen ja USJC:n (United Semiconductor Japan) tutkijat. Niiden yhdessä kehittämä piiri operoi 0,6 voltilla eli lähellä kynnysjännitettä.

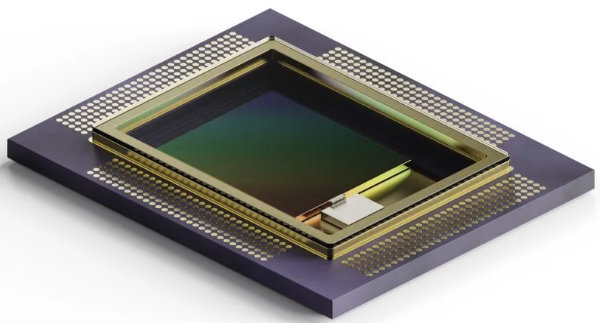

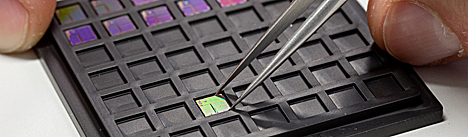

Siru on valmistettu USJC:n ja sopimusvalmistaja UMC:n 55 nanometrin C55DDC-prosessissa. Tämä prosessi on räätälöity pienen tehon hallintaan. Piiri hyödyntää icyflex-V -ydintä, jossa on 256 kilotavua RAM-muistia ja 4 kilotavua ROM-muistia.

Alhainen tehonkulutus perustuu ABB-tekniikkaan (Adaptive Body Biasing). Tämän menetelmän avulla se voi toimia tehokkaasti kaikissa tiloissa - päällä, valmiustilassa ja pois päältä - minimoiden virtavuodot, kun prosessori ei ole käynnissä. Se tarjoaa myös parhaan mahdollisen suorituskyvyn, kun prosessori on aktiivinen.

CSEM:n järjestelmäpiirien tutkimuspäällikkö Stephane Emeryn mukaan monissa sovelluksissa prosessori on käyttämättömänä ja odottaa ulkoista tapahtumaa ennen kuin se herää ja käsittelee tietoja. - ABB-tekniikka pienentää virtavuotoja näinä aikoina. Sen avulla prosessorit voivat toimia erittäin tehokkaasti, kun ne käynnistyvät, Emery kuvaa.