Moni odottaa nyt vesi kielellä ensimmäisiä PCI Express 5.0 -tekniikkaa tukevia läppäreitä, mutta yritysten katse on jo seuraavassa PCIe-sukupolvessa. EDA-ja IP-yritys Cadence Design Systems kertoo, että sen PCIe6-liitännän PHY-osa on viety piille TSMC:n viiden nanometrin N5-prosessissa.

IP:n saaminen piille on aina tärkeä etappi, kun uutta tekniikkaa yritetään saada valmistettavaan kuntoon. Cadencen mukaan TSMC:n valmistama testipiiri on erittäin lupaava, sillä se vastaa uuden standardin vaatimuksiin.

Testipiiri koostu DSP-pohjaisesta PHY-osasta sekä ohjaimesta. Piirin sähköiset ominaisuudet toimivat erinomaisesti kaikilla PCIe-nopeuksilla. Signaloinnista huolehtiva PAM4/NRZ-lähetinosa tuotti eheää, symmetristä signaalia, jonka värinä oli erittäin alhainen.

Testipiirin PCIe6-linkki kesti häiriöitä ja kanavahäviöitä 35 desibelin verran, kun dataa siirrettiin 64 gigatavua sekunnissa. Cadencen ohjainpiirin tehtävä on huolehtia mahdollisimman suuresta datansiirtonopeudella mahdollisimman pienellä latenssilla.

Arkkitehtuuri tukee 1024-bittistä datapolkua 16 linjalla, jotka operoivat yhden gigahertsin kellotaajuudella. Näin liitännässä päästään 128 gigabitin maksimidatanopeuteen sekunnissa. Tähän verrattuna nykyiset, parhaimmillaan PCIe4-liitäntöjä tukevat koneet tulevat vaikuttamaan antiikkisilta nuhapumpuilta.

PCIe6-standardi valmistui viime vuonna. Sen markkinoille tuloa joudutaan kuitenkin odottamaan vielä useamman vuoden ajan.

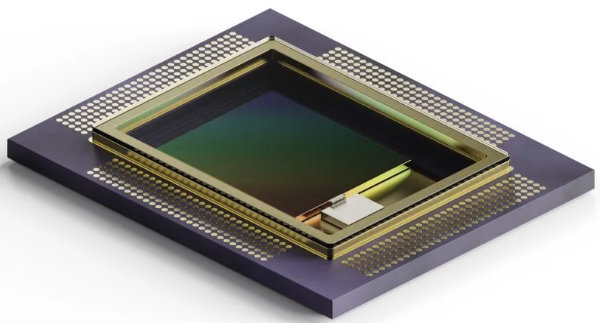

Kuva: TSMC