Puolijohdealan kovimmat kehittäjät ovat tällä San Franciscossa IEDM-konferenssissa, jossa esitellään yritysten uusimpia innovaatioita. Intel hehkutti kokouksessa lisäävänsä jatkossa piiriensä liitäntä- ja kotelointitiheyttä jopa 10-kertaiseksi. Tämä tapahtuu Foveros-pakkaustekniikan uudella Direct-evoluutiolla.

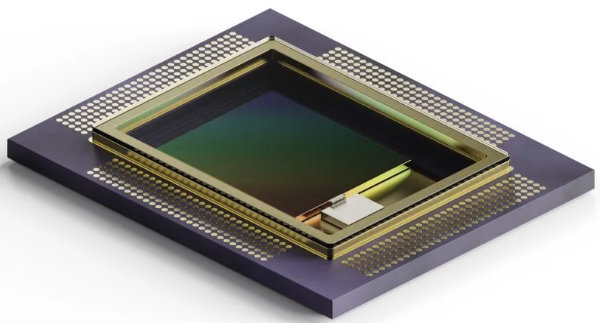

Foveros on muutaman vuoden ajan ollut Intelillä järjestelmäpiirien pakkaustekniikan ytimessä. Nyt tekniikasta on esitelty evoluutioversio, jossa alustan ja piirien väliset liitäntänystyt voivat olla alle 10 mikrometrin kokoisia. Tämä kasvattaa liitäntätiheyden kertaluokkaa suuremmaksi.

Foveros Direct -tekniikan myötä Intel esitti muille kutsun ryhtyä standardoimaan tätä hybridimuotoista kotelointitekniikkaansa. Tarkemmin tekniikkaa esitellään ensi heinäkuussa Intel Accelerated -tapahtumassa.

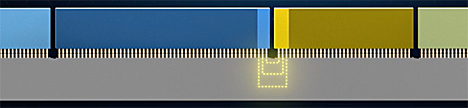

IEDM:ssä Intel myös esitteli ideaansa nykyisten FETtien jälkeiseen aikaan transistoreissa. Yhtiön tavoitteena on pinota CMOS-transistoreita päällekkäin, jolloin logiikkaa voidaan tiivistää 30-50 prosenttia. Samaan suuntaan - siis ylöspäin - transistorien kehityksessä ovat menossa muutkin johtavat puolijohdetalot, tosin strategiat ja uudet rakenteet eroavat hieman toisistaan.

Intel lupaa myös parantaa nykyisten piipohjaisten piirien suorituskykyä uusilla materiaaleilla. Yhtiö on esimerkiksi ensimmäistä kertaa maailmassa integroinut GaN-pohjaisen tehokytkimen suoraan 300-milliselle CMOS-kiekolle. Tämän ansiosta CPU-prosessorille voidaan syöttää virtaa tehokkaammin hyödyntäen galliumnitridin ominaisuuksia: nopeaa kytkentää ja merkittävästi pienempiä tehohäviöitä.