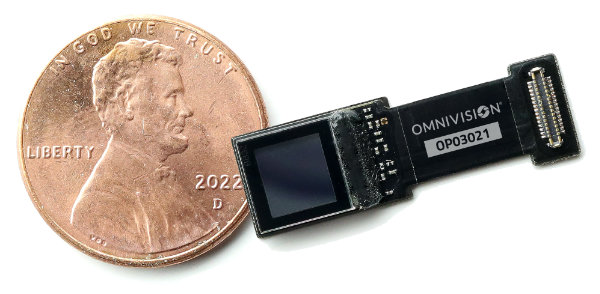

FPGA-valmistaja Xilinx on esitellyt alan ensimmäiset 16 nanometrin prosessissa valmistetut ohjemoitavat sirunsa. Tiheämmän prosessin lisäksi julkistus vie FPGA-piirien teknistä kehitystä eteenpäin monella tapaa. Toimivia siruja Xilinx uskoo saavansa vielä tämän vuoden aikana.

Uusi perhe on nimeltään UltraScale+. Siihen tuodaan sekä high end -pään Virtex-piirit että kustannustehokkaammat Kintex-sirut. Mielenkiintoisin ja edistyksellisin versio on kuitenkin uusi järjestelmäpiiri Zynq. Se vie FPGA-piirien integraation ja suorituskyvyn tasolle, jota ei ole aiemmin nähty.

16 nanometrissä Xilinx tuo uuden muistin FPGA-piireilleen, jota se kutsuu nimellä UltraRAM. IP-lohkot liitetään toisiinsa älykkäästi SmartConnect-liitännällä, joka säästää piialaa merkittävästi ja tehonkulutustakin viidenneksen verran.

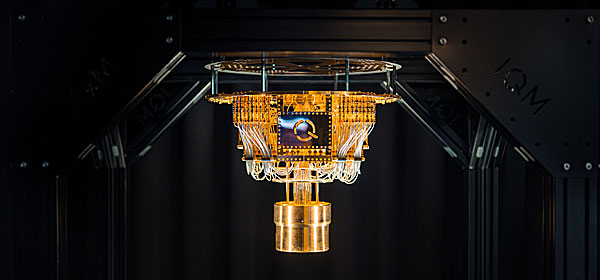

UltraScale+-piirit ovat myös koko puolijohdealan ensimmäiset 3D-transistorirakenteeseen (TSMC:n FinFET) perustuvat sirut, joissa samaan koteloon on pakattu siruja 3D-tyyppisesti. Xilinx kutsuu tätä 3D-on-3D-rakenteeksi.

Uusi Zynq-piiri on tällainen MPSOC-piiri (multisuoritin-järjestelmäpiiri). Enimmillään Zynq-sirulla voi olla neljä 64-bittistä ARM Cortex-A57-ydintä, kaksi 32-bittistä Cortex-R5-ydintä huolehtimassa reaaliaikatehtävistä sekä Mali-400MP-prosessori piirtämässä grafiikkaa. Kun piirille voidaan myös asentaa ohjelmistopohjaisia prosessoreja, suoritimia voi olla yhteensä satoja.

Tulos on vakuuttava. Suorituskyky wattia kohden kasvaa 2-5-kertaiseksi sovelluksesta ja piirin konfiguraatiosta riippuen.

Xilinx sanoo saaneensa TSMC:ltä testipiirejä jo pitkään. Ensimmäinen kokonainen UltraScale+-piiri viedään piille vielä tuotantolinjaan vielä kesään mennessä ja vuoden loppuun mennessä yhtiöllä on käsissään toimivia 16 nanometrin siruja.