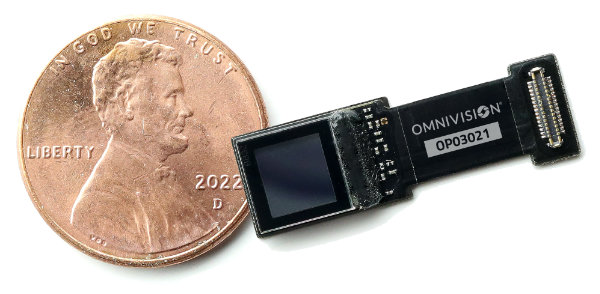

Xilinx ilmoitti tänään, että se on saanut piille ensimmäisen 20 nanometrin prosessissa valmistetun Virtex Ultrascale -piirinsä. Ensimmäisellä uuden sukupolven Virtexillä on 940 tuhatta logiikkasolua.

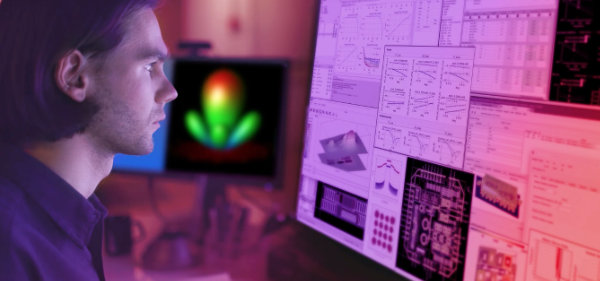

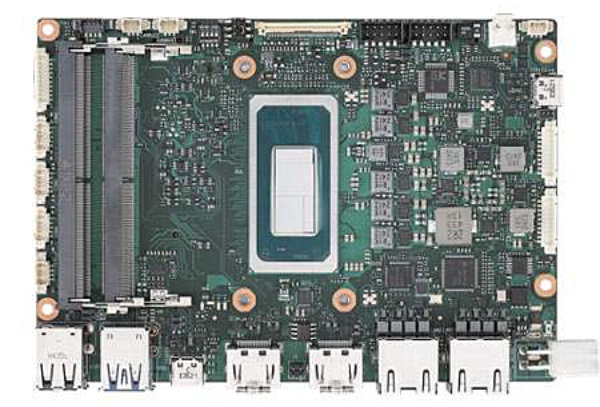

Ohjelmoitavan logiikan lisäksi Vu095-sirulla on kuusi 150 gigabitin Interlaken- ja neljä sadan gigabitin ethernet-ydintä. Taustalevyjärjestelmiin piiri tarjoaa markkinoiden ensimmmäisen ohjelmoitavan 28 gigabittiä sekunnissa siirtävän yhteyden.Ultrascale on paljon enemmän kuin aiempaa tiheämpi viivanleveys. 3D-rakenne ja siitä kaiken suorituskyvyn irti ottaminen on vaatinut aivan uuden suunnittelumetodologian kehittämisen. Se kiteytyy uusissa Vivado-työkaluissa.

Xilinsin mukaan Vivadon kehittäminen kesti neljä vuotta ja vaati tuhannen miestyövuoden panostuksen. Projektina kyse on suurin yksittäinen työkalujen kehityshanke koko puolijohdealalla, yritys uskoo.

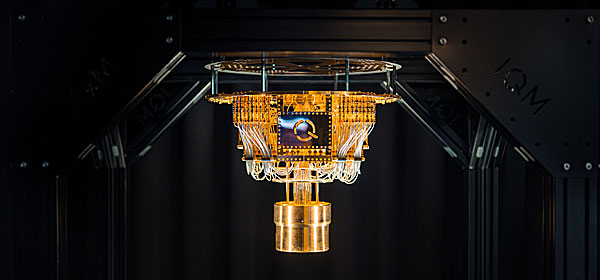

Ultrascale-arkkitehtuuri ratkaisee ennen kaikkea suurimman tiheiden piirien suunnitteluongelmat eli liitännät. 3D-piireissä hyödynnetään uutta SSI-tekniikkaa (Stacked Silicon Interconnect), jonka avulla kaiken ohjelmoitavan logiikan elinikä pitenee, vaikka Mooren lain loppu puolijohteissa jo häämöttääkin. 3d-pinoamisen avulla suurimpien piirien kapasiteetti kasvaa kaksinkertaiseksi aina uuden prosessisukupolven myötä.

Uusien Virtex-piirien lippulaiva 4,4 miljoonan ohjelmoitavan logiikkasolun Vu440. Siitä Xilinx lupaa tarjolle vajaan vuoden kuluttua.