Virheenjäljityksen uudet työkalut voivat leikata merkittävästi virheenhaku- ja validointiaikoja sekä tarjota verrattomat mahdollisuudet FPGA-lohkojen tutkimiseen ja hallintaan. Microsemin kehittämän SmartDebug-työkalupaketin avulla suunnittelija voi supistaa kehitystyöhön tarvittavaa aikaa ja kustannuksia, mikä nopeuttaa tuotteen saamista markkinoille.

| Artikkelin kirjoittaja Ted Marena toimii Microsemi-yhtiön FPGA/SoC-tuotteiden markkinointijohtajana. |

FPGA-pohjaisten laitteiden suunnittelijat kohtaavat monenlaisia haasteita saadakseen tuotteensa sujuvasti valmistuslinjalle. Yleensä työ aloitetaan evaluoimalla kehitettävä laite ja toteuttamalla sitten piirien kuvauskielinen (HDL) suunnitelma. Tämän jälkeen laite kootaan valmiiksi, ja lopuksi suoritetaan koko FPGA-osan virheenkorjausproseduuri ennen kuin laite voidaan siirtää tuotantolinjalle.

Nykyään moniin piirisuunnitelmiin soveltuvat useat erityyppiset FPGA-piirit varsinkin sulautetuissa ja teollisuuskohteissa. Monissa tapauksissa päätös FPGA-piirien toimittajan valinnasta tehdään niiden kehitystyökaluihin liittyvän kokemuksen perusteella. Vaikka valinta tämän perusteella olisi harkittua, eräs vieläkin tärkeämpi tekijä kannattaisi ottaa mukaan päätöksentekoon. Sekä ohjelmiston että FPGA-piirien virheenjäljitystyökalujen tulisi olla suunnittelijoiden vakavan harkinnan kohteena. Nykyään monet FPGA-piirien virheenpoistoon tarkoitetut työkalut saadaan piirien toimittajilta, joita ovat esimerkiksi Altera, Microsemi ja Xilinx. Tarjolla on myös joukko älykkäämpiä debug-työkaluja, joita suunnittelijoiden kannattaisi harkita tulevien FPGA-pohjaisten laitteiden evaluointivaiheessa.

Logiikka-analyysi vianhakuun

Kaikki merkittävät FPGA-toimittajat tarjoavat logiikka-analyysiä virheenkorjauksen työvälineeksi. Tämä on toteutettu pienellä logiikkalohkolla, joka käyttää FPGA:n sisäisiä logiikkaelementtejä ja sulautettua muistilohkoa signaalien näytteenoton muodostamiseksi. Suunnittelija voi määrittää, mitä signaaleja näytetään ja valvotaan sekä asettaa liipaisun, joka ilmoittaa logiikka-analysaattorille, millä hetkellä datantallennus tulee aloittaa. Kun logiikka-analysaattori on asetettu valmiuteen, suunnittelijan on ajettava uudelleen synteesivaihe sekä sijoitus- ja reititystiedot niin, että haluttu funktio otetaan huomioon suunnitelmassa. Kun uudelleenkäännös ja uudelleenohjelmointi on tehty, suunnittelija voi aloittaa logiikkasignaalien katselun logiikka-analysaattorin ruudulta.

On tärkeää huomata, että koska nämä signaalit täytyy näytteistää, ne eivät voi tallentaa tietoa suorituskyvystä reaaliaikaisesti. Logiikka-analysaattori kykenee toimimaan vain nopeuksilla, jotka sallivat datan näytteistyksen ja tallennuksen sisäiseen muistiin. Tämän debug-työkalun haittapuoli on, että virhe usein poistetaan tai peitetään, kun suunniteltavaa ohjelmaa käännetään uudelleen. Virhe voi siten poistua, vaikka sen merkitystä ei tarkasti tiedetä. Tämän seurauksena se voi syntyä uudelleen, kun uudelleensijoitus ja -reititysproseduuri ajetaan seuraavan kerran. Toinen heikkous logiikka-analysaattorin kannalta on se, että näytteistys toimii todennäköisesti hitaammin kuin kytkentää suorittavat signaalit, joten huippunopeassa seurannassa dataa ei ehkä kyetä sieppaamaan.

Näistä rajoituksista huolimatta logiikka-analysaattorin avulla voidaan nähdä signaalien tilat liipaisuasetuksiin perustuen, mistä on merkittävästi apua suunnitteluongelmien etsimisessä ja poistossa. Logiikka-analysaattorin käyttö on periaatteeltaan iteratiivisesti toistettava prosessi: suunnittelija katsoo analysaattorilla, mitä tapahtuu, tekee päivityksen ja sen jälkeen ajaa uudelleenkäännöksen. Tämän jälkeen uusia tuloksia tarkastellaan ja prosessia toistetaan yhä uudelleen, kunnes virhe on havaittu. Kuhunkin iteraatiokierrokseen ja kuhunkin erityiseen virheeseen tarvittava aika vaihtelee, eikä kaikkia tapauksia saada edes siepatuksi logiikka-analysaattorin alhaisen näytenopeuden vuoksi.

Virheiden jäljitykseen käytettävien logiikka-analysaattorien rajoitusten vuoksi FPGA-lohkojen ja piirikorttien validointia varten on kehitetty uusia debuggaus-työkaluja. Esimerkiksi Synopsys tarjoaa tähän Identify-nimistä työkalua, joka yhdistää logiikka-analysaattorin toiminnot Synplify-nimiseen synteesityökaluun virheenhaun iteraatioajan lyhentämiseksi. Yhdessä logiikka-analysaattorin kanssa ne tarjoavat teknologisen näkymän piirisuunnitelman sisään ja helpottavat liipaisutoimintojen määrittelyä. Suunnittelija voi myös tehdä suunnitelmaan muutoksia, jotka päivitetään automaattisesti RTL-koodiin (Register Transfer Level).

Sisäisten FPGA-resurssien säästämiseksi Identify-työkalulla voidaan ryhmittäin näytteistää useita signaaleja sekä multipleksoida niitä, mistä on suurta apua virheenetsintäprosessin alkuvaiheessa, kun ongelman todellista aiheuttajaa ei vielä tiedetä. Identify-työkalun vianhakuun tuomista eduista huolimatta sen lähestymistapa sisältää aina vaatimuksen uudelleenkääntämiseen, mikä vaikuttaa alkuperäiseen suunnitelmaan ja vaatii kallista lisäaikaa nopean logiikan ja sitä merkittävästi hitaamman näytteistyksen sovittamiseksi uudelleen yhteen.

Ikkuna FPGA:n sisään

Logiikka-analysaattorin lisäksi todellista hyötyä suunnittelijalle olisi oskilloskoopista, jolla pääsisi näkemään FPGA-lohkon sisään. Se tarjoaisi piirisuunnitelmaan reaaliaikaisen ikkunan, josta nähtäisiin, mitä signaalit todella tekevät. Olisi ihanteellista päästä reaaliajassa mittaamaan signaaleja FPGA-lohkon sisäisissä solmupisteissä sekä pakottaa sisäisille signaaleille erilaisia haluttuja arvoja ja päästä näin tutkimaan muutosten välittömiä vaikutuksia piirilohkon toimintaan. Lisäksi mahdollisuus lukea ja kirjoittaa sisäisiin muisteihin sekä SerDes-lähetin-vastaanottimen mittauspisteisiin olisi myös todella hyödyllistä. Kaikkien näiden toimintojen saaminen käyttöön häiritsemättä kuitenkaan itse FPGA-suunnitelmaa virtaviivaistaisi dramaattisesti virheenhakuprosessia.

Hyvä esimerkki tällaisesta lähestymistavasta on Microsemin kehittämä SmartDebug-työkalusarja. Se on osa Libero SoC -ohjelmistopakettia, jota käytetään yhtiön FPGA-piiriperheille PolarFire, SmartFusion2 ja IGLOO2. SmartDebug-työkalujen avulla suunnittelija voi suorittaa virheenjäljityksen FPGA-lohkolle, muistilohkoille ja SerDes-yksikölle aivan kuin käytössä olisi oskilloskooppi. Työkalujen avulla voidaan hyödyntää erityisiä FPGA-logiikan sisään sijoitettuja mittauspisteitä, mikä merkittävästi nopeuttaa ja yksinkertaistaa virheenhakuprosessia. Tarjolla on myös mahdollisuus valita eri mittauspisteitä tarvitsematta välillä kääntää koodia uudelleen. Edistyneet virheenjäljitysominaisuudet tarjoavat pääsyn mihin tahansa logiikkaelementtiin ja antavat suunnittelijoille mahdollisuuden tarkistaa tulojen ja lähtöjen tilat reaaliajassa. Tärkeimpiä ominaisuuksia, joita voidaan käyttää ilman piirisuunnitelman uudelleensovittamista, ovat:

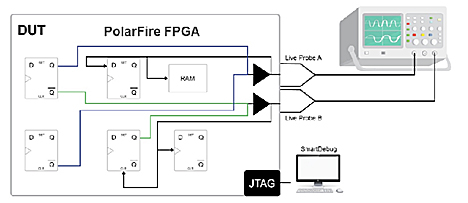

Live Probe: Tämä sallii käyttää enimmillään kahta erikoismittapäätä, jotka voidaan konfiguroida mittaamaan FPGA-logiikkalohkon mitä tahansa solmupistettä kuten tuloa, lähtöä tai logiikkaelementtiä (ks. kuva 1). Datankeruupisteet valitaan mittapäille ohjelmallisesti ja sen jälkeen komento lähetetään kaapelin kautta JTAG-nastoille, minkä jälkeen signaalit nähdään välittömästi oskilloskoopin ruudulla. Mittauspisteet ovat dynaamisia ja reaaliaikaisia. FPGA:n uudelleenkääntämistä tai uudelleenohjelmointia ei tarvita lainkaan, mittauspisteitä voidaan vaihtaa useita kertoja ’lennossa’, ja signaalit ovat välittömästi nähtävissä.

Kuva 1. Esimerkki Live Probe -mittapäiden käytöstä.

Active Probe: Tämä mahdollistaa flip-flop-elementin tai mittauspisteen asynkronisen luvun tai kirjoituksen dynaamisesti. Suunnittelija voi valita FPGA:n rekisterien tai muistilohkojen sijainnit. Tämän ansiosta käyttäjä voi nopeasti havaita logiikan vaikutukset sisäisesti tai testata nopeasti, miten mittauspisteeseen kirjoittaminen vaikuttaa logiikan toimintaan. Mikä tahansa määrä signaaleja voidaan pakottaa tiettyihin arvoihin, ja aivan kuten Live Probe -toiminnossa FPGA:n uudelleenkääntäminen tai uudelleenohjelmointi on tarpeetonta. Toiminto on erityisen käyttökelpoinen silloin, kun halutaan pakottaa piirisuunnitelmaan virheitä ja tutkia, mitkä niiden vaikutukset logiikan toimintaan ovat.

Tyypillisesti suunnittelijat käyttävät vähintään 30 prosenttia ajastaan piirisuunnitelman virheiden etsimiseen. Tämä prosenttiluku voi olla paljon suurempikin riippuen suunnitteluprojektin koosta ja vaiheesta. Esimerkiksi keskikokoisen FPGA-lohkon täydellinen virheenhakuprosessi saattaa kestää viikkoja. Prosessi on tuskallinen, sillä siihen sisältyy lukuisia iteraatiokierroksia, joiden tarkkailtavuus ja hallittavuus on rajoitettua. Tarvitaan toistuvia sijoitus-reititys-operaatioiden uudelleenajoja, ajoitusratkaisuja ja uudelleenohjelmointia.

Älykkäitä virheenjäljityksen työkaluja hyödyntämällä suunnittelijat voivat validoida FPGA-suunnitelmansa paljon nopeammin kuin käyttämällä vain mukaan liitettyä logiikka-analysaattoria. Esimerkiksi PolarFire-sarjan 300K LE -tyyppinen FPGA-piiri voi hyödyntää logiikka-analyysitoiminnon lisäksi aiemmin mainittua oskilloskooppitoimintoa. Sallimalla suunnittelijan katsella signaaleja reaaliajassa ja ohjata niiden tiloja läpi koko piirisuunnitelman päästään merkittävästi nopeampaan virheidenpoistoon.

Useilta asiakkailta on saatu palautetta, että he ovat onnistuneet leikkaamaan virheenhakuaikojaan merkittävästi lyhyemmiksi käyttämällä SmartDebug-työkaluja. Sisäisen logiikka-analysaattorin korvaaminen älykkäällä virheenhakuprosessilla on antanut näille suunnittelijoille mahdollisuuden tunnistaa ongelmakohdat muutamassa tunnissa viikkojen sijasta. Eräässäkin tapauksessa ongelman jäljet johtivat täysin eri moduuliin kuin logiikka-analysaattorilla tutkittaessa oli näyttänyt. Kyseistä piirisuunnitelmaa voitiin vielä edelleen parantaa pakottamalla erilaisia arvoja Active Probe -toiminnon avulla, ja näin piirien asianmukainen toiminta saatiin varmistetuksi.

Edistyneet virheenjäljitysmenetelmät muuttavat koko pelin luonnetta FPGA-suunnittelijoiden kannalta. Uusimmat ratkaisut voivat leikata merkittävästi virheenhaku- ja validointiaikoja sekä tarjota vertaa vailla olevat mahdollisuudet FPGA-lohkon tutkimiseen ja hallintaan. Suunnittelijoiden kannattaakin vakavasti miettiä FPGA-lohkon virheenhakumahdollisuuksia ennen kuin valitsevat piirejä tuleviin suunnitelmiinsa. Oikea valinta voi merkittävästi vähentää kehitystyöhön tarvittavaa aikaa ja kustannuksia, mikä nopeuttaa tuotteen saamista markkinoille.