Markkinoilla vasta valmistaudutaan PCIe-väylän 5.0-versioon, mutta suunnittelutalo Synopsys sanoo kehittäneensä ensimmäisen IP-ratkaisun, jolla voidaan kehittää tulevaa PCIe 6.0 -standardia tukevia järjestelmäpiirejä.

PCISIG-järjestö julkisti uuden standardin viimeisen version jo kuukausia sitten, mutta lopullinen standardi on vasta valmistumassa. Se saataneen muutaman kuukauden sisällä. Lopullisesta draftista standardin sisältö ei kuitenkaan ole muuttumassa.

Tämän takia IP-lohkoja piireille tarjoava EDA-talo Synopsys on lanseerannut markkinoiden ensimmäiset IP-ytimet, joilla voidaan kehittää sekä PCIe 6.0 -ohjain, liitännän fyysinen kerros, ja IP-sen testaamiseen.

Käytännössä paketti on tarkoitettu 5 nanometrin järjestelmäpiirien suunnitteluun. Niihin saadaan nyt varmennettu väylä, joka tukee PCIe 6.0 -nopeuksia.

Laitteiden kannalta tämä tarkoittaa 64 gigasiirtoa jokaisen PCIe-linjan yli. Kun standardi tukee 16x-konfiguraatiota, saadaan PC-järjestelmässä siirrettyä dataa 128 gigatavua sekunnissa molempiin suuntiin samanaikaisesti.

Tämä tarkoittaa nelinkertaista nopeutta esimerkiksi nykyisiin PCIe 4.0 -väyläisin SSD-levyihin verrattuna, ja kaksinkertaista nopeutta vasta markkinoille tulossa oleviin PCIe 5.0 -laitteisiin verrattuna. Kaikki IP-ytimet kuuluvat Synopsysin DesignWare-kirjastoon.

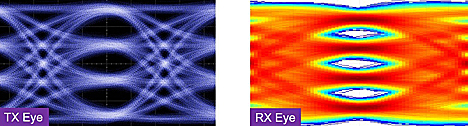

PCIe 6.0 hyödyntää PAM4-signalointia. Kuvassa Synopsysin esitys PCIe 6.0 -lähetys- ja vastaanotetun signaalin silmäkaaviosta.