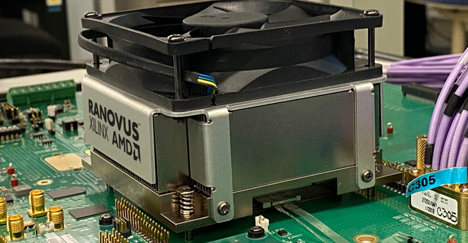

Internet-liikenteen määrä kasvaa tunnetusti eksponentiaalista vauhtia. Tämä asettaa jatkuvasti kasvavia haasteita datakeskusten verkkokorteille ja -prosessoreille. Ranovus lupaa korjata ongelman integroidulla prosessorin ja optisen vastaanottimen yhdistelmällä. Nyt tekniikkaa on ensimmäistä kertaa demottu FPGA-pohjaisella verkkokortilla.

Ranovus esitteli viime vuoden puolella Odin-piirin, joka on yhtiön mukaan toisen polven CPO-suoritin. CPO tulee sanoista Co-packaged optics. Odin 2.0 kykenee prosessoimaan 800 gigabitin datalinjaa erittäin alhaisella latenssilla ja protokolla-agnostisesti.

Demossa piiri on integroitu AMD:n nyt omistaman Xilinxin FPGA-piirin kylkeen. Tai oikeammin ACAP-piirin kylkeen. ACAP viittaa adaptiiviseen laskennallisen kiihdytyksen alustaan, joka on karkeasti ottaen FPGA-pohjainen, pitkälle tiettyä sovellusta varten räätälöity prosessosointijärjestelmä.

Odin-piirillä voidaan toteuttaa esimerkiksi ethernet-liitäntä, joka skaalautuu 800 gigabitistä aina 3,2 terabittiin sekunnissa. Laite välittää PAM4signaoidun datan ethernet-kytkimelle ja koneoppimis- ja tekoälymalleja laskevalle piirille yhdessä ja samassa kotelossa. Tämä vähentää merkittävästi koko järjestelmän kustannuksia ja virrankulutusta.

Motiivi Odinin kaltaiselle piirille, jolle on integroitu optinen moottori, on helppo ymmärtää. Nykyisellä datakasvulla datakeskusten tehonkulutus kasvaa vauhdilla, joka tekee koko yhtälöstä mahdottoman 5-10 vuoden aikana.