DRAM-muistien nopeus ja niiden käyttämät väylät ovat kehittyneet nopeasti, mutta eivät riittävän nopeasti. Tämän takia avoin CXL-liitäntä eli Compute Express Link tulee korvaamaan sen monissa sovelluksissa. Nyt CXL on päivittynyt versioon 3.0

CXL perustuu PCI Express -väylän fyysiseen kerrokseen, jonka yli ajetaan erityistä CXL-protokollaa. PCIe-väylä mahdollistaa nopean ja alhaisen viiveen yhteyden isäntäprosessorin ja erilaisten laitteiden, kuten kiihdyttimien, muistipuskurien ja I/O-laitteiden, välillä.

CXL-väylää kehittää erillinen yhteenliittymä, CXL Consortium. Se julkisti tekniikan 2.0-version marraskuussa. Ensimmäinen 1.0-standardi julkistettiin maaliskuussa hieman yli kaksi vuotta sitten, joten CXL-väylän kehitys on ollut nopeaa. Mukana ovat olleet kaikki datakeskusten laitteiden parissa työskentelevät yritykset, sillä palvelimissa korttien väylät ovat kiistatta pahin pullonkaula. Perinteiset DRAM-ratkaisut eivät enää täytä nykyvaatimuksia.

CXL 3.0 nostaa väylän nopeuden 32 gigasiirtoon sekunnissa eli kaksi kertaa 2.0-edeltäjää nopeammaksi. Fyysisessä kerroksessa PCIe-versio vaihtuu samalla 6.0:een, jonka nopeus on 64 gigasiirtoa sekunnissa. 16 linjaa pitkin PCIe6 yltää siis 128 gigatavuun sekunnissa. Tämä perustuu pitkälti uuteen PAM4-signalointiin.

CXL Consortiumin mukaan väylän nopeus on nostettu kaksinkertaiseksi ilman, että latenssi on edellispolvesta kasvanut. Keskeistä koko CXL-väylässä on kuitenkin ns. koherenssi. Siinä CPU pystyy samalla nopeudella hyödyntämään kaikkia tallennusvälineitä, jotka on liitetty laitteet PCIe-väylään. 3.0-version julkistamisesta kestänee aikaa ennen kuin ensimmäiset sitä tukevat laitteet tulevat markkinoille. CXL Consortium ei edes esitä tästä mitään aika-arviota.

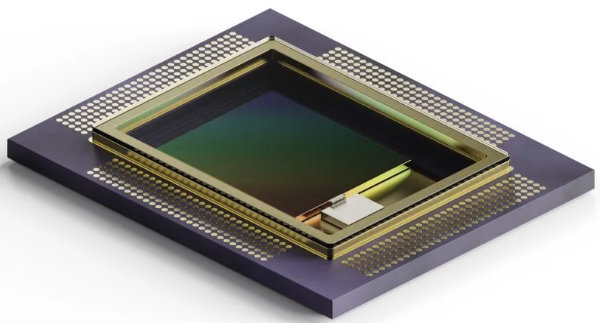

Kuvassa Samsungin reilu vuosi sitten esittelemä ensimmäinen muistimoduuli, joka tuki CXL-standardia.