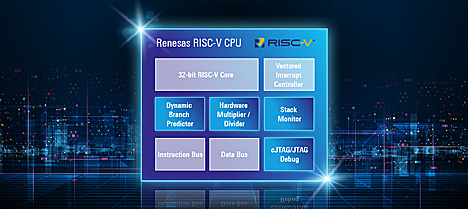

Berkeleyn yliopistossa kehitetty avoin RISC-V-arkkitehtuuri on saavuttanut nopeasti suosiota sulautetuissa sovelluksissa, mutta ohjaimien ykkössarjaan kuuluva Renesas Electronics on nyt ottanut merkittävän askeleen ensimmäisenä isona MCU-talona. Se on esitellyt ensimmäisen oman RISC-V-prosessorinsa.

32-bittinen uutuus tulee yleiskäyttöisten mikro-ohjaimien markkinoille. Kohdealueisiin Renesan luettelee IoT-laitteet, kulutuselektroniikan, terveydenhuollon ja teollisuuden laitteet ja järjestelmät. RISC-V CPU ydin täydentää Renesasin nykyistä 32-bittisten mikro-ohjainten valikoimaa, johon jo kuulkuvat yhtiön omat RX-piirit sekä Arm Cortex-M -arkkitehtuuriin perustuvat RA-perheet.

Renesasin ensimmäinen avoimeen käskykantaan perustuva CPU on monipuolinen, soveltuu erilaisiin sovelluksiin ja on tehokas piialueen käytössä, mikä vähentää käyttö- ja vuotovirtaa. Se tarjoaa myös korkean laskentatehon sulautetuille järjestelmille.

Renesas ei ole ensimmäistä kertaa RISC-V-vankkurien kyydissä Yhtiö on aiemmin kehittänyt 32-bittiset ääniohjaus- ja moottorinohjauspiirit sekä 64-bittiset RZ/Five 64-bittiset yleiskäyttöiset mikroprosessorit. Ne kehitettiin kuitenkin Andes Technologyn prosessoriytimille.

Renesasin RISC-V -suoritin saavuttaa vaikuttavan 3,27 CoreMark/MHz -suorituskyvyn, mikä ylittää markkinoiden samanlaiset arkkitehtuurit. Se sisältää laajennuksia, jotka parantavat suorituskykyä ja pienentävät koodin kokoa. Yhtiö aikoo julkaista ensimmäisen RISC-V-pohjaisen MCU-piirin ja siihen liittyvät kehitystyökalut vuoden 2024 ensimmäisellä neljänneksellä.

Lisätietoja täällä.