Mooren laille on ennustettu kuolemaa jo pitkään, mutta ainakin toistaiseksi turhaan. Eikä loppua ole vieläkään näkyvissä. Belgialainen mikroelektroniikan tutkimuslaitos IMEC on jo esitellyt PDK-suunnittelualustat 2 nanometrin sirujen suunnittelun aloittamiseksi.

Mooren laille on ennustettu kuolemaa jo pitkään, mutta ainakin toistaiseksi turhaan. Eikä loppua ole vieläkään näkyvissä. Belgialainen mikroelektroniikan tutkimuslaitos IMEC on jo esitellyt PDK-suunnittelualustat 2 nanometrin sirujen suunnittelun aloittamiseksi.

ISSCC-konferenssissa esitellyt PDK-paketit tulevat Cadencen ja Synopsysin EDA-työkaluja. Samalla IMEC lanseerasi 2N-prosessiin fokusoidun EUROPRACTISE-koulutusohjelman. Tämä antaa korkeakouluille ja teollisuudelle välineet kouluttautumiseen tulevaisuuden puolijohdeasiantuntijoita ja mahdollistaa teollisuuden siirtää tuotteensa seuraavan sukupolven teknologioihin.

Koulutusohjelmassa tulevaisuuden suunnittelijat oppivat N2:n erityispiirteet. Koulutus keskittyy Cadencen ja Synopsysin digitaalisen suunnittelun ohjelmistoihin.

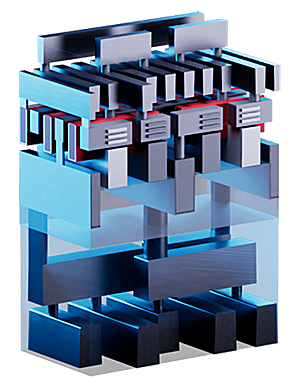

IMECin 2N-prosessi perustuu GAA-rakenteeseen GAA viittaa transistorirakenteeseen, jossa hila ympäröi kanavaa kokonaan. Valmistajista Samsung sanoo siirtyvänsä samaan rakenteeseen 2 nanometrin prosessissa, mutta TSMC on tuomassa rakennetta jo 3 nanometrin piireihin.

Toinen uusi idea N2-siruilla on tehonsyöttö transistorirakenteen takapuolella. Tämän pitäisi ratkaista aiempiin FinFET-rakenteisiin liittyvät ongelmat vuotovirtojen osalta.

IMECin roadmapissa N2-prosessia seuraa A7, jossa viivanleveys on 0,7 nanometriä.