![]() Suunnittelutiimien on oltava varovaisia määrittäessään, mitä flash-piirejä ja tiheyksiä käyttävät sovelluksissaan, koska ajan myötä ja käytöstä riippuen ne kuluvat. Nykypäivän flash-muistit ovat siirtyneet pois monikiteisen piin kelluvan hilan tekniikasta piinitridikennoihin, joihin varaukset vangitaan. Tämä tarkoittaa, etteivät vanhat suunnittelun mallit ja säännöt enää ole voimassa.

Suunnittelutiimien on oltava varovaisia määrittäessään, mitä flash-piirejä ja tiheyksiä käyttävät sovelluksissaan, koska ajan myötä ja käytöstä riippuen ne kuluvat. Nykypäivän flash-muistit ovat siirtyneet pois monikiteisen piin kelluvan hilan tekniikasta piinitridikennoihin, joihin varaukset vangitaan. Tämä tarkoittaa, etteivät vanhat suunnittelun mallit ja säännöt enää ole voimassa.

|

Artikkelin on kirjoittanut Axel Störmann, joka toimi Kioxialla muistien markkinoiden ja suunnittelun johtajana. |

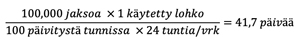

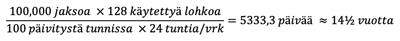

Huolimatta siitä, että flashia käytetään lähes kaikissa sulautetuissa järjestelmissä, niissä tehdään edelleen virheitä, jotka usein saavat paljon julkisuutta. Nämä ongelmat johtuvat liiallisesta kirjoitus/poisto-syklien määrästä, jotka johtavat jopa tuotteiden takaisinkutsuihin turvallisuusongelmien takia. Tuotekehitysprosessin alkuvaiheessa tiimin on arvioitava näiden W/E-käyttöjen (write/erase) säännöllisyys ja kirjoitettavan datan määrä. Tätä verrataan sitten mahdollisten flash-muistien datakirjoihin. Yksinkertaisessa, hallitsemattomassa NAND-piirissä, jolle tarjotaan 100 000 W/E-sykliä muistilohkoa kohden, 100 päivityksen kirjoittaminen tunnissa joka päivä yhteen lohkoon antaisi käyttöiän:

Hajauttamalla kirjoitettua dataa useille muistilohkoille, muistin eliniän odote kasvaa merkittävästi:

Tämä lähestymistapa W/E-kuorman jakamiseen useiden flash-muistilohkojen välillä tunnetaan kulumisen tasoittamisena (wear leveling). Sulautetuissa järjestelmissä, joissa ei ole tiedostojärjestelmää, kehitystiimin on otettava käyttöön sopiva lähestymistapa ohjelmistossa. Sivun poispyyhkiminen tyhjentää kaikki muistisolut arvoon 1, kun taas kirjoittaminen varaa 0-bitin. Käyttämällä osittaisena ohjelmointina tunnettua ominaisuutta yksi flash-muistisivu voidaan kirjoittaa rajoitetun määrän kertoja ilman, että solut pyyhitään 0:aan. Dynaaminen kulumista tasoittava lähestymistapa voi käyttää tätä ominaisuutta datalohkojen merkitsemiseen tai taggaamiseen mitätöidyksi (invalid) sen jälkeen, kun uusin versio datasta on kirjoitettu uudelle sivulle. Tämä lähestymistapa edellyttää loogista lohkon osoitusta (LBA, logical block addressing) eli taulukkoa, joka ylläpitää muistissa linkkiä kirjoitettujen tiedostojen ja niiden todellisen fyysisen sijainnin välillä.

Kulumisen tasoittamisen ymmärtäminen

Jos osaa samasta flashista käytetään staattisen datan, kuten käynnistyslataimen tai sovelluskoodin tallennukseen, nämä muistisivut eivät kulu juuri lainkaan. Edistyneemmät kulumista tasaavat lähestymistavat siirtävät staattista dataa uusiin sijainteihin, jolloin niihin liittyvät muistisivut voivat pidentää flash-muistin yleistä käyttöikää. Linuxia käyttävät sovellukset hyötyvät tiedostojärjestelmistä, jotka integroivat kulumisen tasoituksen hallitsemattomaan NAND-tallennukseen. Tällaisia ovat esimerkiksi JFFS2 ja YAFFS.

Muita flash-tallennuksessa huomioitavia seikkoja ovat ympäristö ja nopeus. Flashin kestävyys ja datan säilyminen määritetään tyypillisesti 40 °C:ssa, mutta nämä luvut laskevat nopeasti nousseissa lämpötiloissa. Nykypäivän kompaktit, kannettavat laitteet voivat tehdä lämmönhallinnasta piirikorttitasolla haastavaa, joten on tärkeää ymmärtää tarkasti se lämpötila, joka flash-piiriin voi kohdistua. Muistilohkojen pyyhkimiseen kuluva aika kasvaa kulumisen myötä, joten kovien reaaliaikaisten sovellusten suunnittelijoiden tulee myös huomioida lohkojen enimmäispyyhkimisajat.

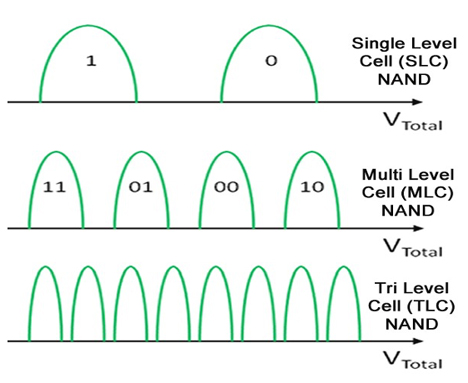

Kun flashin suosio räjähti vaihtoehtona pyörivälle levytallennukselle ja älypuhelimet ja tabletit tulivat markkinoille, kustannustehokkaamman flash-tekniikan tarve kasvoi. Pelkästään litografian tuomaan kutistumiseen luottaminen rajoitti maksimitiheyttä. Sen sijaan, että tallennettaisiin yksi bitti solua kohden, joka tunnetaan nimellä single level cell (SLC), otettiin käyttöön kaksi bittiä (multilevel cell tai MLC) (kuva 1). Vaikka tämä tyydytti kuluttajien vaatimuksen kohtuuhintaisesta suuren kapasiteetin säilytystilasta, heikentynyt W/E-kestävyys oli merkittävä huolenaihe teollisuuden ja autoteollisuuden sovelluksissa.

Kuva 1: Nykypäivän NAND-flash-muisti tallentaa useita bittejä solua kohden yhden bitin sijaan.

3D-flashtekniikka

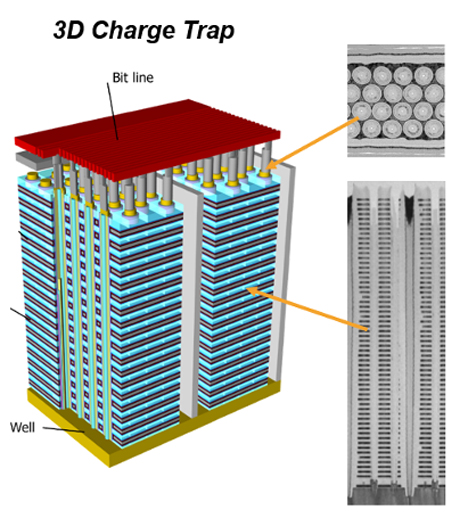

Siitä lähtien tallennustiheyden on pyritty kasvattamaan käyttämällä 3D-valmistustekniikoita, kuten KIOXIAn BiCS FLASH (Bit Column Stacked, kuva 2). Rakentamalla pystysuoria flash-muistisolurakenteita, jotka näyttäisivät mikroskoopilla korkealta rakennukselta, tallennustiheyttä rajoittavat rakenteen korkeus yhdistettynä sirun pinta-alaan. Siirtyminen tasomaisista kelluvan hilan FG-soluista pystysuuntaisiin piinitridipohjaisiin CT-kennoihin tarjoaa lisäetuja. Koska kunkin solun pinta-alan pienentämiseen on vähemmän tarvetta, CT-solut voivat olla suurempia kuin FG-solut. Suurempi koko mahdollistaa suuremman varauksen tallentamisen ja yksinkertaistaa MLC- ja kolmebittisten solujen (TLC) tallennustoteutusta. Kun solujen välinen etäisyys on suurempi, myös solujen välisen ylikuulumisen mahdollisuus pienenee, mikä mahdollistaa nelitasoiset QLC-solut. Kioxian BiCS5 yltää 112 kerrokseen, joten yksisiruisia flash-muisteja, kuten THGJFHT3TB4BAIF UFS-piiri, on nyt saatavana 1 teratavun tallennuskapasiteetilla.

Kuva 2: Kioxian BiCS FLASH 3D -flashmuistitekniikka kasvattaa NANS-tallennuksen tiheyttä lisäämällä kerrosten määrää ja soluun tallennettujen bittien määrää.

Yleisesti ottaen CT-kennoihin perustuva flash sietää paremmin jatkuvien W/E-jaksojen aiheuttamia vikoja. Datan säilytyskyky on kuitenkin hieman alhaisempi kuin FG-muisteissa, mikä kompensoituu hallitun NAND-flash-tuotteen sulautetun ohjaimen tai asianmukaisen ulkoisen ohjaimen vahvemmalla virhetarkistuksella (ECC).

Koska 3D-flash-muistit ovat TLC-tyyppiä, teollisuuden ja autoteollisuuden käyttäjät joutuvat ajan myötä siirtymään siihen. 3D-flashin erilaisista ominaisuuksista johtuen on todennäköistä, että myös monet sovellukset joutuvat siirtymään hallittuihin NAND-ratkaisuihin sen sijaan, että kehittäisivät omia kulumisen tasoitusohjelmistoja hallitsemattomaan NANDiin.

Hallittuja NAND-flash-vaihtoehtoja ovat e-MMC (embedded Multimedia Card) ja UFS (Universal Flash Storage). e-MMC tunnetaan ehkä parhaiten, koska ydinteknologia on ollut markkinoilla 20 vuotta. Useimmissa järjestelmäpiireissä on sisäänrakennettu tuki fyysiselle liitännälle, joten ne on helppo integroida suunnitteluun. Uusimmat JEDEC 5.0/5.1 -standardin mukaiset piirit voivat saavuttaa jopa 400 MB/s tiedonsiirtonopeuden ja sisältävät ECC-virheenkorjauksen, kulumisen tasoittamisen ja huonojen lohkojen hallinnan. JEDEC-standardi määrittelee myös joukon rekistereitä, jotka tarjoavat tietoja kulutetuista W/E-jaksoista ja jäljellä olevista varalohkoista. Tämä on merkittävä etu verrattuna hallitsemattomaan NANDiin, joka ei tarjoa tällaisia rekistereitä tai odotettavissa olevaa elinkaaren dataa ja vaatii siten ulkoisen ohjaimen.

Yksibittinen pseudopiiri

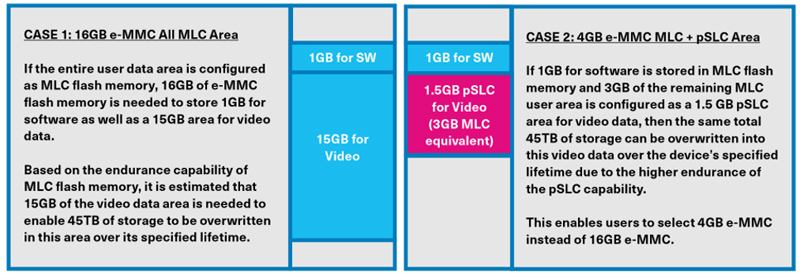

Sulautetut MLC- ja TLC-pohjaiset MMC-laitteet voidaan konfiguroida pseudo-SLC (pSLC) -osiolla kestävyydestä, tietojen säilyttämisestä ja kirjoitussuorituskyvystä kiinnostuneiden tarpeisiin. Tämä vähentää solua kohden tallennetun datan 1 bittiin, mikä vähentää MLC-kapasiteetin puoleen (kaksi bittiä yhteen) ja TLC-kapasiteetin kolmasosaan (kolme bittiä yhteen). Tämän seurauksena pSLC-tila voi sallia 5–10 kertaa enemmän W/E-syklejä kuin mikä olisi muuten mahdollista natiivilla MLC:llä tai TLC:llä.

pSLC voi myös vähentää saman sovelluksen toteuttamiseen tarvittavaa kokonaistallennuskapasiteettia. Työkuorma-analyysi voi esimerkiksi osoittaa, että 45 teratavun videodatan tallentamiseen tuotteen määritetyn käyttöiän aikana. Tarvitaan 15 gigatavua MLC-muistia. Yhdessä 1 gigatavun ohjelmiston kanssa tämä vaatisi 16 Gt e-MMC-tilaa. Jos käytetään pSLC-osiota sama työmäärä vaatii 1,5 gigatavun osion MLC-tallennustilasta. Tämä vähentää laitteen tarvitseman kokonaiskapasiteetin vain 4 gigatavuun (kuva 3).

Kuva 3: Pseudo-SLC:n eli pSLC:n käyttö (pSLC) parantaa MLC-piirin datankestävyyttä. Se sekä parantaa ML-muistin datan pysyvyyttä, että voi pienentää saman työkuormaan vaatimaa piirin kapasiteettitarvetta puhtaaseen MLC-muistiin verrattuna.

Viimeisimpään SSD-tekniikkaan verrattuna sulautetun flashin käyttäjät valittavat kulumisesta ja laitteen käyttöiän kestävistä datasta. Vaikka tämä ei todennäköisesti muutu e-MMC:n osalta, JEDEC vastaa tähän tarpeeseen UFS-laitestandardeissa. UFS on nykyaikainen tekniikka ja korkeampi siirtonopeus (2,33 Gt/s), täyden kaksipuolisuuden tuki ja parannettu energiatehokkuuden myötä UFS on suositeltu hallittu NAND-ratkaisu, kun vaaditaan yli 32 Gt:n kapasiteettia, ja valittu SoC sisältää liitännän.

Lopuksi

Markkinavoimat ovat painostaneet NAND-flash-valmistajia toimittamaan entistä suurempia tiheyksiä käyttämällä uusinta, huippuluokan liitäntätekniikkaa. Siirtyminen 3D NAND -flashiin on jo pitkällä, joten perinteiset hallitsemattomat SLC NAND -laitteet ja ohjelmistojen kulumisen tasoittamisen kehittäminen jäävät vähitellen menneisyyteen. Taso- ja 3D-flashin teknisten erojen vuoksi kulumista tasaavien ohjelmistojen kehittämistä tarvitsevien on tehtävä tiivistä yhteistyötä valmistajien kanssa tarvittavien algoritmien kehittämiseksi. Useiden bittien tallennus solua kohden on nykypäivän NAND-flashille jo standardi. Niille, jotka haluavat parantaa kestävyyttä ja säilytysikää, pSLC on kuitenkin usein hyväksyttävä vaihtoehto. Hallitut NAND- muistit, kuten e-MMC ja UFS, yksinkertaistavat toteutuksia huomattavasti, mutta tällaisten piirien käyttö vaatii silti huolellista arvioitua elinkaaren työkuormien analysointia sen varmistamiseksi, että haihtumaton tallennustila ei kulu ennenaikaisesti.