CPLD-piirien (Complex Programmable Logic Device) arkkitehtuurissa on tapahtunut viime vuosina lukuisia muutoksia, jotka laajentavat huomattavasti tämäntyyppisten komponenttien sovellusalaa ja hämärtävät CPLD- ja FPGA-piirien välistä rajaa.

| Artikkelin on kirjoittanut Digi-Keyn tekninen suunnittelija Rich Miron. Hän on työskennellyt Digi-Keyllä vuodesta 2007 lähtien, mitä ennen hän työskenteli Bechtel Bettisillä vanhempana suunnittelijana. Richillä on elektroniikkainsinöörin tutkinto Pohjois-Dakotan yliopistosta. |

CPLD-piirien ja FPGA-piirien arkkitehtuurissa on kuitenkin ratkaisevia eroja, joiden vuoksi CPLD-pohjaiset laitteet soveltuvat erityisen hyvin tiettyihin käyttötarkoituksiin.

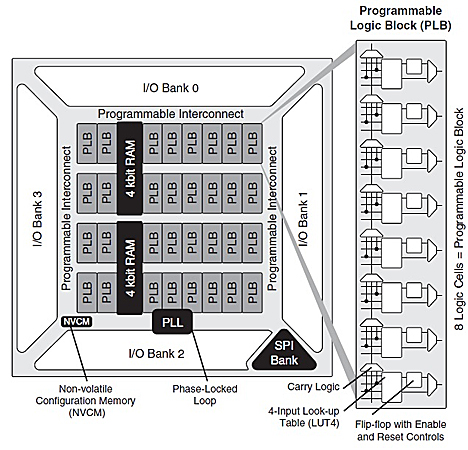

Perinteisesti CPLD- ja FPGA-piirien erot ovat perustuneet suurimmaksi osaksi sisäiseen arkkitehtuuriin. Vanhassa CPLD-arkkitehtuurissa, joka perustui käyttäjän ohjelmoitavissa olevan logiikan varhaisiin muotoihin eli alhaisen integraatiotason PLA-piireihin, perustana oli tulotermilohkojen ryhmä, jota käytettiin reititysmatriisin kautta.

Klassisten CPLD-piirien arkkitehtuurissa logiikkapolkujen reitit ovat varsin deterministisiä. Jokaisessa logiikkamatriisin ylityksessä viive on aina sama. Laitteiden koon kasvaessa reititysarkkitehtuuri alkaa kuitenkin kuluttaa kohtuuttoman paljon resursseja. Samalla kun yleinen trendi alkoi suosia erittäin suuren mittakaavan integraatiota, suunnittelijat pyrkivät kehittämään laitteiden kapasiteettia. Kysyntään vastatakseen CPLD-piirien valmistajat ottivat käyttöön täysin toisenlaisen lähestymistavan, jossa hyödynnettiin eräitä FPGA-piireissä käytettyjä konsepteja, mutta niitä muokattiin CPLD-piirien tyypillisiin käyttökohteisiin paremmin sopiviksi.

Keskeisiä muutoksia oli kaksi. Näistä ensimmäinen oli hajautettuun reititysarkkitehtuuriin siirtyminen, jolloin logiikkapolkujen ei tarvitse kulkea koko sirun yli, vaan ne voivat käyttää logiikkaryhmien lohkojen välisiä reittejä, jotka on järjestetty matriisiksi koko mikropiirissä. Toinen muutos oli tulotermiryhmien korvaaminen LUT-hakutaulukoilla (look-up tables), jolloin saadaan käyttöön neljää syötettä käyttävät ohjelmoitavat totuustaulut, jotka ohjaavat kiikkua.

Uudempien CPLD-piiriperheiden joustavamman logiikka-arkkitehtuurin ansiosta logiikan syntetisoinnissa voidaan käyttää korkean tason suunnittelukieliä, joita ovat esimerkiksi Verilog ja VHDL. Hajautettu reititysarkkitehtuuri voi kuitenkin vaikeuttaa ajoittamista piirikaaviotasolla (schematic) suunnitellun logiikan ennakoinnissa. Näitä laitteita käytettäessä sijoittelu on kuitenkin varsin vapaata, jolloin aikasensitiivisten logiikkapolkujen allokointi on mahdollista, mutta muiden logiikkapolkujen automaattisessa sijoittelussa ja reitittämisessä voidaan silti hyödyntää edistyneitä suunnittelutekniikoita, rajoituksia ja määritelmiä. Lisäksi ylätasolla tapahtuvan pinnien suunnittelun ja lukituksen ansiosta on mahdollista suunnitella PCB- ja CPLD-logiikat samanaikaisesti, millä saadaan nopeutettua projektien läpimenoaikoja.

Nykyisissä CPLD-piireissä on ominaisuuksia, jotka kuuluivat alun perin FPGA-piireihin, mutta niissä on myös edelleen tiettyjä erityispiirteitä, joiden vuoksi ne soveltuvat tiettyihin käyttökohteisiin FPGA-piirejä paremmin. CPLD-piirit eivät todellakaan ole vain pienempikokoisia FPGA-piirejä.

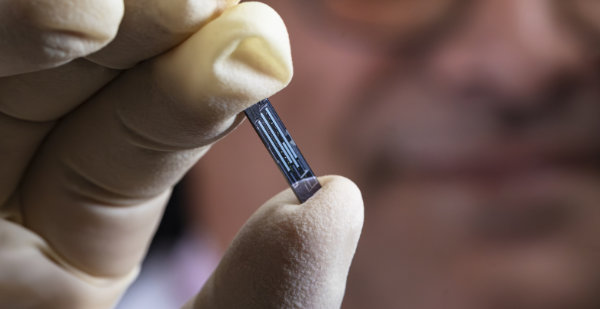

CPLD-piirien keskeisenä etuna useimpiin FPGA-piireihin verrattuna on, että ne käyttävät konfigurointitietojen tallentamiseen sisäistä haihtumatonta muistia. Muutamia poikkeuksia lukuun ottamatta FPGA-piireissä käytetään sisäistä SRAM-muistia, joten käynnistettäessä konfigurointitiedot on aina ladattava ulkoiselta levyltä tai flash-muistista. Sisäisen haihtumattoman muistin käytöstä saadaan kahdenlaista etua.

Näistä ensimmäinen on turvallisuus. Jos valmistuksen jälkeen laite lukitaan konfigurointitietojen lukemisen estämiseksi, väärentäjän tai kloonaajan on huomattavasti hankalampaa saada selville sisällä olevan logiikan rakenne. FPGA-piireissä konfigurointitiedot voidaan lukea bittivirrasta, joka kulkee PCB:n kautta ulkoisesta muistista logiikkalaitteeseen. Tosin monet tuotteet tukevat nykyään bittivirran salausta, mikä vähentää tietojen kopioinnin todennäköisyyttä.

Toinen etu on, että CPLD on toimintavalmis heti käynnistettäessä. Monet tiheämmät CPLD:t suorittavat sisäisen kopioinnin sisäisestä flash-muistista SRAM-pohjaisiin konfigurointisoluihin. Näin tehdään mahdolliseksi piirien tuottaminen perinteisillä CMOS-prosesseilla. Haihtumattomia muistisoluja ei tarvitse jakaa koko logiikkaryhmän alueelle, jolloin niiden valmistaminen on helpompaa. Tässäkin tapauksessa konfigurointi tapahtuu kuitenkin millisekunneissa, ja useissa sovelluksissa ominaisuudet ovat käytössä käytännössä heti.

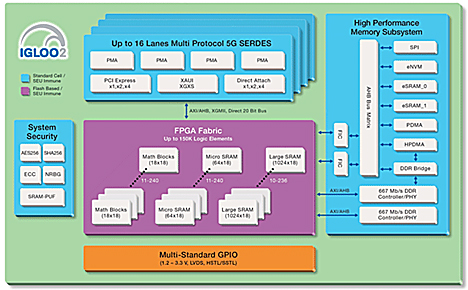

Esimerkiksi Microsemin valmistamassa IGLOO2-piiriperheessä hyödynnetään ainutlaatuista prosessia, jossa flash-muistisolut voidaan upottaa tavanomaiseen CMOS-logiikkaan. Konfigurointitiedot tallennetaan itse kytkinmatriisiin, jolloin konfigurointi ei vie lainkaan ylimääräistä aikaa. Laite voidaan sammuttaa kokonaan, kun järjestelmä on lepotilassa, jolloin jännitteen palautuessa virtaa ei tarvitse kuluttaa uudelleenkonfigurointiin.

Kuva 1. IGLOO2-lohkokaavio (lähde: Microsemi)

IGLOO2-laitteita käytettäessä järjestelmän suunnittelija päättää, säilytetäänkö haihtuvat rekisterin ja sisäisen muistin sisällöt, kuten viestiliikenteen puskureiden tiedot. Jos tiedot halutaan säilyttää, tämä vie jonkin verran virtaa. Vaihtoehtoisesti järjestelmä voidaan suunnitella niin, että laitteen virta voidaan sammuttaa kokonaan, jolloin virran palatessa tarvittavat tiedot palautetaan haihtumattomasta muistista.

FPGA-piirejä alhaisempi virrankulutus myös tiheää logiikkaa käytettäessä on toinen syy, miksi CPLD-tyyppinen laite voi olla monissa tapauksissa järjestelmän suunnittelun kannalta parempi valinta. Lattice Semiconductorin ICE40-perhe suunniteltiin mobiililaitteisiin ja muihin alhaisen virrankulutuksen sovelluskohteisiin. Laitteen arkkitehtuurin ominaisuuksia ovat esimerkiksi ohjelmoitavat pienen vaihteluvälin differentiaali-I/O:t, mahdollisuus sammuttaa sisäiset PLL-piirit dynaamisesti sekä erikoistuneet salvat, jotka jäädyttävät tiettyjen syötteiden tilan energian säästämiseksi. Nämä ominaisuudet edistävät staattisen ja dynaamisen virrankulutuksen hallintaa, jolloin tuoteperheen kaikkien jäsenten staattinen virrankulutus on erittäin pieni.

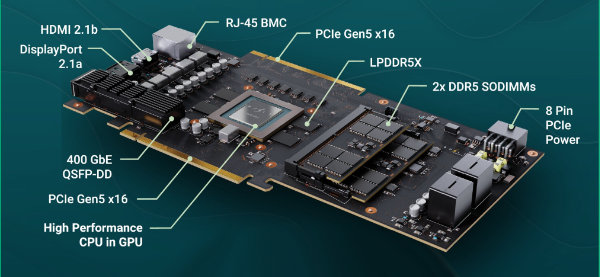

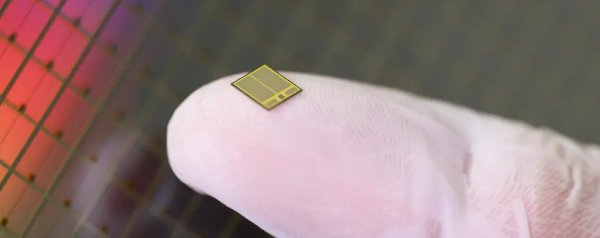

Kuva 2. Latticen ICE40 FPGA (lähde: Lattice Semiconductor)

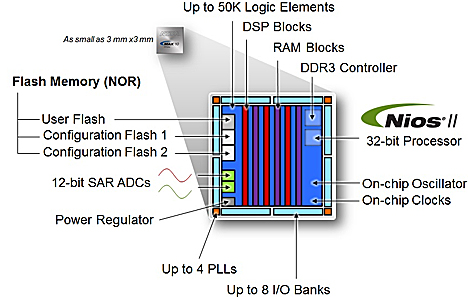

Analogista I/O:ta käyttävissä tuoteperheissä, kuten Alteran Max10-piireissä ohjelmoitava FPGA-piiri korvaa mikroohjaimet useissa eri sovelluskohteissa, etenkin sellaisissa, joissa tarvitaan suorituskykyistä reaaliaikaista tiedonkäsittelyä ja erittäin joustavaa I/O:ta. Max10-mallissa on 12-bittinen yhden meganäytteen sekunnissa näytteistävä AD-muunnin, joka voi käsitellä jopa 17 tulokanavaa.

Kuva 3. Tyypillinen Altera Max 10 FPGA.

Nopealla mukautetulla logiikalla voidaan myös rakentaa analogisia I/O-toimintoja, joita voidaan käyttää esimerkiksi näppäimistön dekoodauksessa. Esimerkiksi Altera Maxissa voidaan edullisen ulkoisen kondensaattorin lisäämisellä käyttää sisäisen oskillaattorin ja Schmitt-laukaisimen I/O-ominaisuuksia, jolloin muunnos analogisesta digitaaliseen voidaan tehdä sarjaliikennemuunninta hyödyntävän topologian avulla.

Mikro-ohjainta käyttävä ohjelmoitava logiikkalaite sopii myös sovelluksiin, joissa I/O-liitäntöjen välillä tarvitaan jännitetason muuntamista. Mikro-ohjaimella tämä on hankalaa, sillä niissä I/O-resurssien määrä on rajallinen ja usein käytössä on vain yksi jännitelähde. CPLD-piireissä on sen sijaan useita I/O-liitäntöjä, jotka on yleensä ryhmitelty lohkoihin (bank). Jokaiseen I/O-lohkoon voidaan liittää oma jännitelähde. Näin yleisten oheislaitteiden, esimerkiksi LCD-näyttöjen, käyttämiseen tarvitaan vähemmän komponentteja.

CPLD-tyyppisillä laitteilla voidaan myös ylläpitää I/O:t pienellä teholla ja tehdä yksinkertaisia päivityksiä, joten ne sopivat erittäin hyvin kohteisiin, joissa energiankulutuksella on paljon väliä, ja joissa on jatkuvasti päivitettävä LCD-tilanäyttöjä ja vastattava näppäimistökomentoihin. Jos järjestelmään tarvitaan tämän lisäksi mikro-ohjain sitä voidaan pitää horrostilassa pidempään. Tämä säästää kriittistä tehoa, kun monet toiminnot voidaan siirtää energiatehokkaammalle ohjelmoitavalle logiikalle.

Toinen piirre, jonka CPLD-tyyppiset laitteet ovat alkaneet omaksua FPGA-piireiltä upotetun käsittelyn avuksi, on aritmeettinen kiihdytys. Esimerkiksi Max10-tuoteperheessä on nykyään versioita, joiden hajautetuilla laitetason kerroinyksiköillä voidaan tukea korkeaa suorituskykyä vaativia digitaalisia signaalinkäsittelytoimintoja. Lisäksi LUT-pohjaiset logiikkalohkot esimerkiksi ICE40:ssä tukevat carry chain -ketjuja. Näiden avulla voidaan esimerkiksi summainpiirit toteuttaa tehokkaasti.

Aritmeettisen kiihdytyksen sekä nopean I/O-prosessoinnin tuen yhdistelmä tekee näistä ohjelmoitavista logiikoista sopivia esimerkiksi moottorin ohjauksen kaltaisiin sovelluksiin. Logiikkalohkoilla voidaan toteuttaa esimerkiksi pulssileveysmodulaation (PWM) kaltaisia toimintoja, jotka mikro-ohjaimen ohjelmistolla ajettuna ovat hyvin käskyintensiivisiä.

Laitetason kertoimien ja muiden moduulien lisäämisen ansiosta CPLD- ja FPGA-piirien välinen ero on hämärtynyt, ja monista entisistä CPLD-tuoteperheistä on nyt tullut käytännössä haihtumatonta muistia käyttäviä FPGA-piirejä. Ominaisuuksiensa ansiosta ne kuitenkin soveltuvat kohteisiin, joissa ne muodostavat edullisemman ja virtapihimmän vaihtoehdon sekä mikro-ohjaimille että kalliimmille FPGA-piireille.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.