Käytännössä Codasip myy halvemman pään RISC-V-prosessorisuunnittelunsa yhdysvaltalaiselle puolijohdeyhtiölle ja siirtyy kehittämään ratkaisuja, joissa turvallisuus rakennetaan suoraan piiritasolle. Kaupan on määrä toteutua noin kuukauden kuluessa.

Liikkeen taustalla on selvä markkinamuutos. Perinteiset RISC-V-ytimet ovat muuttumassa perushyödykkeiksi, joita saa useilta toimittajilta – osin myös avoimena lähdekoodina. Tällaisessa ympäristössä erottautuminen pelkällä CPU-ytimellä on yhä vaikeampaa.

Codasip hakee kasvua arkkitehtuuritason turvallisuudesta. Yhtiö panostaa CHERI-malliin (Capability Hardware Enhanced RISC Instructions), jossa muistiturva ja käyttöoikeudet toteutetaan suoraan prosessorin käskykannassa. Tavoitteena on estää haavoittuvuuksia jo ennen kuin ne syntyvät ohjelmistotasolla.

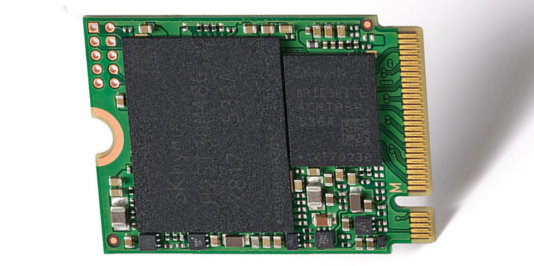

Samalla yhtiö laajentaa tarjontaansa yksittäisistä ytimistä kokonaisiin järjestelmiin. Tulossa on CHERI-pohjaisia järjestelmäpiirejä ja FPGA-ratkaisuja, joilla asiakkaat voivat rakentaa turvallisuuskriittisiä sovelluksia infrastruktuuriin, pilveen ja julkishallintoon.

Strateginen käännös kertoo laajemmasta ilmiöstä. RISC-V International -ekosysteemissä perusarkkitehtuuri on vakiintumassa, mutta arvo siirtyy yhä enemmän sen päälle rakennettuihin ominaisuuksiin.