FPGA tuo joustavuutta, suorituskykyä ja konfiguroitavuutta teollisuuden järjestelmiin. Moottorien ohjauksessa FPGA-logiikalla on monia etuja puolellaan.

|

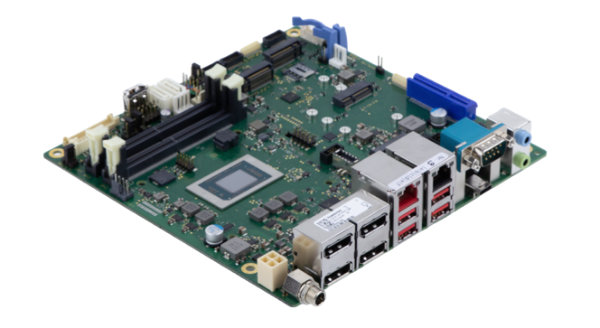

Nykyaikaisten teollisuusjärjestelmien suunnittelijat kohtaavat monia haasteita. Järjestelmistä tulee monimutkaisempia, standardit muuttuvat, suorituskykyä halutaan koko ajan lisää ja kustannuksia pitäisi silti alentaa. Suunnittelijat voivat käyttää FPGA-piirejä oheisprosessoreina, älykkäinä I/O-liitäntöjen lisäämisen komponentteina erillisen prosessorin rinnalla, tai kokonaisina yhden sirun SoC-ratkaisuna.

FPGA-logiikan avulla suunnitteluun voidaan lisätä uusia liitäntöjä ja suorituskykyistä logiikkaa - ja näitä ominaisuuksia voidaan konfiguroida milloin tahansa! FPGA-piireillä voi olla ohjelmistopohjaisia prosessoreja (kuten Alteran Nios II -suoritin), tai niillä voi olla kovakoodattu prosessoriydin, kuten Alteran Cyclone V SoC-piirillä. Näillä siruilla kovakoodattu prosessori on kaksiytiminen ARM Cortex A9, jonka kellotaajuus yltää 925 megahertsiin asti.

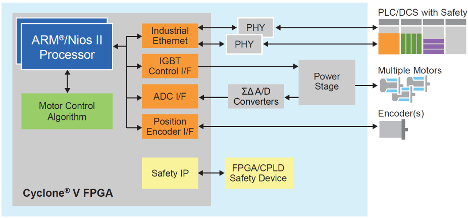

Kuva 1 esittää tyypillistä FPGA-pohjaista moottorinohjausjärjestelmää. Oranssilla kuvatut liitäntälohkot on toteutettu FPGA-logiikalla, joten järjestelmään voidaan toteuttaa mikä tahansa sen vaatima liitäntä. Graafisella Qsys-työkalulla liitäntä voidaan myös milloin tahansa muuttaa. Tämän ansiosta räätälöityjä järjestelmäratkaisuja voidaan luoda hyvin nopeasti.

Kuva 1 - FPGA-pohjainen moottorinohjausjärjestelmä

Kun käyttää FPGA-logiikan IP-lohkoja, voi valita sarja- rinnakkais- ja sigma-delta-ADC-liitäntöjen väliltä, erilaisia digitaalisia enkoodereita, räätälöityjä PWM-ulostuloja, jotka sopivat valittuun IGBT-moduuliin tai sovellukseen, sekä laajasta valikoimasta sopivan teollisuuden Ethernet- tai Fieldbus-liitännän. Kaikki tämä voidaan tehdä ilman, että järjestelmään lisätään laitteita tai käytetään rahaa kortin uudelleensuunnitteluun. Suunnittelu on myös jatkossa helpompi päivittää esimerkiksi standardin muuttuessa: riittää että FPGA-konfiguraatiota muutetaan ja päivitetään.

Jos ohjausta, tietoliikennettä ja järjestelmänhallintaa pitää ajaa mikro-ohjaimella tai DSP-prosessorilla, niiden suorituskyky ei yleensä riitä kaikkeen. FPGA:n avulla järjestelmään voidaan lisätä ohjelmistopohjainen prosessori tai käyttää kovakoodatun Cortex-A9:n suurta suorituskykyä, jotka tulevat SoC-piirille vain pienen lisäkustannuksen kera. Jos joku prosessi vaatii kaiken kovakoodatun prosessorin tehon, voidaan järjestelmään aina lisätä softapohjainen Nios II -prosessori tukemaan moottorinohjausta, kun Cortex-A9 ajaa käyttöjärjestelmää tai järjestelmän jotain muuta paljon suorituskykyä vaativaa osaa.

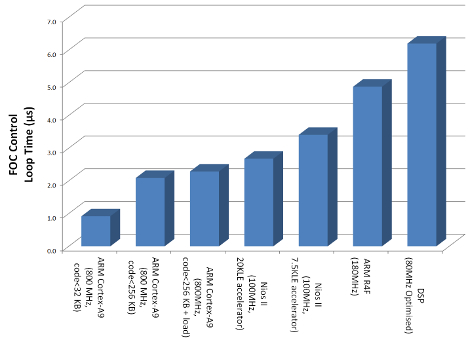

Kuvassa 1 näkyvä vihreä lohko on laitteistopohjainen kiihdytysmoduuli, jonka tehtävä on lisätä Nios II -prosessorin suorituskykyä kenttäväyläohjatun moottorin algoritmien prosessoinnissa. Kuvassa 2 näkyy erilaisten ratkaisujen tyypillinen suorituskyky. Cortex-A9 ja kiihdytetty Nios II tuovat erinomaisesti tehoa perinteisiin ratkaisuihin verrattuna.

Kuva 2 - Erilaisten järjestelmien suorituskyky kenttäväyläohjatussa luupissa (FOC).

Perinteiset ratkaisut riittävät , jos tarvitaan vain yksinkertainen moottorinohjausratkaisu. FPGA:n arvo tulee järjestelmäkustannusten alentamisesta integroinnin myötä ja joustavuuden lisääntymisenä, kun voidaan tukea laajaa valikoimaa liitäntöjä sekä suunnitteluvaiheessa että tuotannon jälkeen. ARM Cortex-A9:n lisääminen järjestelmäpiirille nostaa tämän arvon uudelle tasolle, kun yhdellä ainoalla FPGA-piirillä voidaan tarjota mahdollisuus tukea järjestelmän ydinprosessoritoimintoja, joita yleensä ajetaan Linuxin, Windows Compactin tai VxWorksin kaltaisilla käyttöjärjestelmillä.

FPGA tuo merkittävän hyödyn myös suorituskykyyn. Jos moottorinohjaussovellus vaatii suurta suorituskykyä/tehokkuutta, pitää kontrolliluupin taajuutta lisätä, jotta viive roottorin ja kenttäohjaimen generoiman magneettikentän välillä lyhenisi. Kuten kuvasta 2 näkyy, FPGA-pohjainen ratkaisu voi tuoda selvästi perinteistä ratkaisua enemmän suorituskykyä, erityisesti mikäli resursseista ei ole pulaa. Tämä nopea ohjaus on hyödyllinen myös muissa invertteripohjaisissa sovelluksissa kuten aurinkopaneeleissa ja tuulivoimaloiden inverttereissä, jotka syöttävät sähkövirtaa takaisin verkkoon. Erityisen hyödylliseksi nopeus tulee järjestelmissä, jotka vaativat yhden sirun moniakseliratkaisun: FPGA-piirille voidaan rakentaa täysin rinnakkaiset ohjausjärjestelmät ilman, että ohjausluupin aika pitenee riippumatta siitä, kuinka monta akselia toteutuksessa on.

Käytännössä järjestelmän pitää pohjautua realistiseen suunnitteluun, jossa kustannukset pysyvät aisoissa. Tämä tarkoittaa resurssien jakamista akselien kesken. Onneksi tämä voidaan helposti toteuttaa FPGA-piirillä, erityisesti mikäli käytetään Alteran DSP Builderin kaltaista automatisoitua työkalua. DSP Builderin avulla ohjausalgoritmi voidaan toteuttaa Matlab Simulinkissä, jossa Qsys-työkalussa käytettävä kiihdytysmoduuli generoidaan automaattisesti. Ennen kuin logiikka luodaan DSP Builderissa, voidaan halutun optimoinnin taso valita niin, että FPGA-resurssit ja suorituskyky voidaan tasapainottaa omien vaatimusten mukaan.

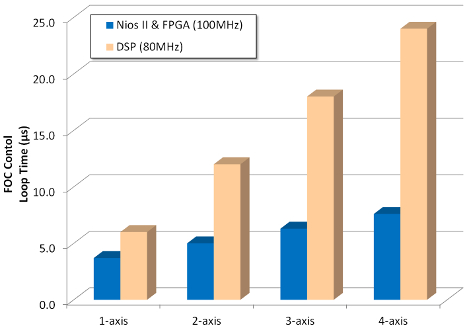

Kuva 3 - Optimoitujen moniakseliratkaisujen vertailu FPGA:ta ja DSP:tä käytettäessä

Kuvassa 3 on vertailtu FPGA- ja DSP-pohjaisia moniakseliohjauksia. Kuten voi odottaa, akselien lisääminen pienentää DSP:n suorituskykyä hieman. DSP prosessoi kiinteällä nopeudella, joten akselien määrän kaksinkertaistaminen kaksinkertaistaa myös kontrolliluupin aikaa (DSP:n pitää laskea kaksi luuppia, yksi kummallekin akselille, kellojaksoa kohti). Sen sijaan FPGA-piirillä DSP Builder osaa rakentaa kontrolliluuppien kesken tehokkaasti jaetun liukuhihnalogiikan, mikä ei juuri kasvata prosessointiaikaa. Tämä toteutus optimoi myös suunnittelun koon. Järjestelmässä on vain yksi Nios II -prosessori, joten akseleille tulee pieni lisäviive, kun prosessori noutaa dataa, käynnistää kiihdyttimen ja prosessoi lähtödatan jokaiselle akselille.

FPGA:n joustavuus ja suorituskyky ja Cortex-A9-prosessorin lisääminen auttaa kehittämään integroituja järjestelmäratkaisuja, joita vielä muutama vuosi sitten ei osattu edes kuvitella.

Virtaamamittaus on monissa laitteissa kriittinen mutta usein ongelmallinen toiminto. Perinteiset mekaaniset anturit kuluvat ja jäävät sokeiksi pienille virtausnopeuksille. Ultraäänitekniikkaan perustuvat valmiit moduulit tarjoavat nyt tarkan, huoltovapaan ja helposti integroitavan vaihtoehdon niin kuluttaja- kuin teollisuussovelluksiin.

Virtaamamittaus on monissa laitteissa kriittinen mutta usein ongelmallinen toiminto. Perinteiset mekaaniset anturit kuluvat ja jäävät sokeiksi pienille virtausnopeuksille. Ultraäänitekniikkaan perustuvat valmiit moduulit tarjoavat nyt tarkan, huoltovapaan ja helposti integroitavan vaihtoehdon niin kuluttaja- kuin teollisuussovelluksiin.