Suomesta tulee harvoin innovaatioita puolijohdealalle, mutta espoolainen Pixpolar yrittää tehdä näin uudella logiikkateknologiallaan. Se perustuu JFET-rakenteeseen eli kanavatransistoriin, jolla on monia etuja puolellaan perinteiseen CMOS-pohjaiseen logiikkaan verrattuna.

Tekniikan on kehittänyt Pixpolarin perustaja Artto Aurola. Hänen mukaansa tekniikalla voidaan toteuttaa eri logiikkajännitepareja toisin kuin CMOS-logiikalla. Lisäsi tekniikka sopii toteutettavaksi millä tahansa puolijohdemateriaalilla.

- JFET-transistoriin perustuvan logiikan tehonkuutus olisi vähintään yhtä alhainen kuin CMOS-logiikalla, sillä tekniikka eliminoi pitkälle hilan vuotovirran ja kanavan vuotovirran, Aurola selostaa.

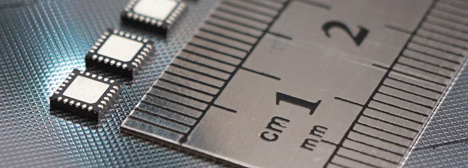

Yhden MOSFETin korvaamiseen tarvitaan kaksi JFETiä, joten sirutasolla uusi logiikkateknologia vie enemmän pinta-alaa. Lisäksi yksittäinen MOSFET saadaan puristettua pienempään tilaan kuin JFET. - Näin ollen tietty uudella logiikkateknologialla toteutettu piiri vie selvästi enemmän sirupinta-alaa kuin vastaava CMOS-logiikalla toteutettu piiri. Uudella logiikkateknologialla voidaan kuitenkin toteuttaa jännitetason säätöä, mitä ei oikein voi toteuttaa nykyisellä CMOS-logiikalla. Näin ollen uudella logiikkateknologialla on mahdollista integroida logiikkalohkoihin sellaisia toimintoja, jotka nykyisellään toteutetaan piirilevyillä, Aurola sanoo.

FPGA-piiri voisi tällöin toimia jonkun toiminnon protoalustana ilman erillisät piirikorttia.

JFETin yksi tärkeä etu CMOS-logiikkaan verrattuna on merkittävästi parempi säteilynkesto. Tämän ansiosta tekniikka sopisi erinomaisesti esimerkiksi avaruusteknologian logiikkakomponenttien toteutukseen.

- MOS-rakenne on huono säteilyn keston kannalta esimerkiksi siksi, että säteily muuttaa transistorin kynnysjännitettä vaikuttamalla hilaeristeen pysyvän varauksen määrää. Toisaalta säteily voi aiheuttaa hilaeristeen läpi johtavan kanavan, joka pahimmillaan aiheuttaa oikosulun. JFETin kynnysjännite ei ryömi lainkaan joten säteily ei ole mikään ongelma.

Aurola on patentoimassa tekniikkaansa, eikä tutkimuksen mukaan esteitä patentoinnille ole. Hänen mukaansa puolijohdevalmistajat eivät ole tähän asti halunneet käydä aktiivisesti neuvotteluja tekniikan kaupallisesra hyödyntämisestä. - Ilmeisesti nyt on meneillään asemasotavaihe, jossa tutkitaan patenttihakemuksia, joita käytettäisiin myöhemmin pelimerkkeinä ristiinlisensiointisopimusneuvotteluissa, Aurola arvioi.

Aurola itse arvioi, että ensimmäisenä tekniikkaa tullaan hyödyntämään avaruuskäyttöön suunnatuilla logiikkapiireilä.

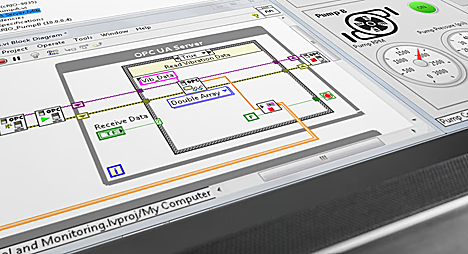

Englantilainen Pickering Interfaces esitteli Electronica-messuilla uuden sukupolven yksipaikkaisen sulautetun PXIe-ohjaimensa mallimerkinnältään 43-920-002. Uutuus on markkinoiden kompaktein ja tehokkain 3U-ohjain PXI Express -alustalle.

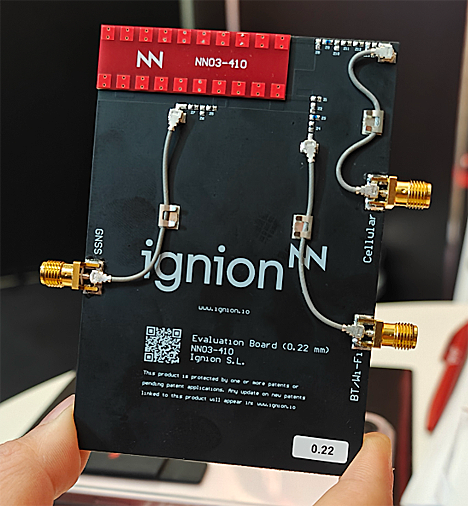

Englantilainen Pickering Interfaces esitteli Electronica-messuilla uuden sukupolven yksipaikkaisen sulautetun PXIe-ohjaimensa mallimerkinnältään 43-920-002. Uutuus on markkinoiden kompaktein ja tehokkain 3U-ohjain PXI Express -alustalle. Barcelonalainen ignion esitteli Electronica-messuilla uutta OMNIA mXTEND -komponenttiaan, joka yhdistää kolme antennia yhteen innovatiiviseen ratkaisuun. Virtuaaliseksi antenniksi kutsuttu moduuli muuttaa piirikortin kolmen eri radion säteileväksi antenniksi.

Barcelonalainen ignion esitteli Electronica-messuilla uutta OMNIA mXTEND -komponenttiaan, joka yhdistää kolme antennia yhteen innovatiiviseen ratkaisuun. Virtuaaliseksi antenniksi kutsuttu moduuli muuttaa piirikortin kolmen eri radion säteileväksi antenniksi.

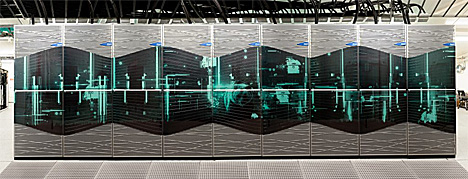

ETNdigi 2/2024 -lehti käsittelee laajasti elektroniikka-alan innovaatioita, erityisesti sulautettuja järjestelmiä ja kehittyvää tekoälyä. Lehdessä esitellään esimerkiksi LUMI-supertietokoneen roolia tekoälymallien kehittämisessä Suomessa. Uutiskattauksen lisäksi mukana on useita syvemmälle eri tekniikoihin sukeltavia artikkeleita.

ETNdigi 2/2024 -lehti käsittelee laajasti elektroniikka-alan innovaatioita, erityisesti sulautettuja järjestelmiä ja kehittyvää tekoälyä. Lehdessä esitellään esimerkiksi LUMI-supertietokoneen roolia tekoälymallien kehittämisessä Suomessa. Uutiskattauksen lisäksi mukana on useita syvemmälle eri tekniikoihin sukeltavia artikkeleita.