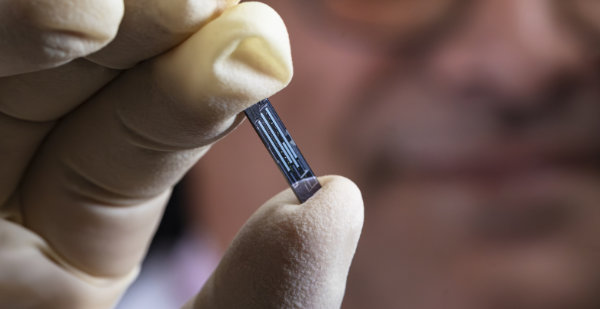

Ohjelmoitava FPGA-piiri mahdollistaa pitkälle viedyn, tehokkaan rinnakkaisen laskennan. Eniten tehoa siitä saadaan, mikäli ohjelmointi tehdään standardoidulla OpenCL-kielellä.

Artikkelin kirjoittaja tohtori Deshanand Singh toimii pääsuunnittelijana Alteran  teknologiakeskuksessa Torontossa. Hän johtaa Alteran OpenCL-to-FPGA -projektia vastaten erityisesti korkean tason suunnittelutyökaluista. Niiden avulla suunnittelijat voivat kehittää sovelluksia FPGA-piireille aiempaa tuottavammin. Aiemmin Singhin tiimi tuotti optimointialgoritmeja Altera Quartus II -työkaluihin. Tohtori Singhillä on ajoitustekniikoiden (timing closure) alueelta tutkinto toronton yliopistosta. Hänellä on yli 50 patenttia ja julkaisua FPGA-tekniikassa. teknologiakeskuksessa Torontossa. Hän johtaa Alteran OpenCL-to-FPGA -projektia vastaten erityisesti korkean tason suunnittelutyökaluista. Niiden avulla suunnittelijat voivat kehittää sovelluksia FPGA-piireille aiempaa tuottavammin. Aiemmin Singhin tiimi tuotti optimointialgoritmeja Altera Quartus II -työkaluihin. Tohtori Singhillä on ajoitustekniikoiden (timing closure) alueelta tutkinto toronton yliopistosta. Hänellä on yli 50 patenttia ja julkaisua FPGA-tekniikassa. |

Ohjelmoitavien tekniikoiden alkuaikoina oli kaksi ohjelmoitavuuden ääripäätä. Toista edusti yksiytiminen CPU tai DSP-prosessori. Näitä laitteita ohjelmoitiin ohjelmistolla, joka koostui listasta suoritettavia käskyjä. Käskyjä luotiin tavalla, joka oli ohjelmoijan näkökulmasta sarjamuotoinen. Edistynyt prosessori pystyi kyllä uudelleen järjestelemään käskyjä niin, että ajonaikana päästiin käskytasolla rinnakkaisuuteen.

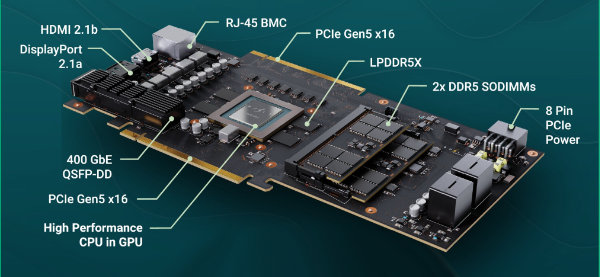

Toisen ääripään ohjelmoitavuudessa muodosti FPGA. Näitä piirejä ohjelmoidaan luomalla konfiguroitavia laitetason piirejä, jotka suorittavat käskyjä täysin rinnakkain. FPGA-suunnittelija luo itse asiassa hyvin hienojakoista rinnakkaista sovellusta. Monien vuosien ajan nämä kaksi ääripäätä elivät rinnakkain ja niitä käytettiin eri sovellusalueilla. Tekniikan skaalautumisen viimeisimmät trendit ovat suosineet kuitenkin lähestymistapoja, jotka ovat sekä ohjelmoitavia että rinnakkaisia.

Toinen trendi, mihin ohjelmoitavat piirit nojasivat, oli monimutkaisen raudan tuleminen, jolla käskytason rinnakkaisuutta voitaisiin ajaa sarjamuotoisista ohjelmista. Yksiytiminen arkkitehtuuri saisi syötteenä sarjan käskyjä ja suorittaisi ne piirillä, jolla olisi monia rinnakkaisia toiminnallisia yksiköitä. Iso osa prosessoriraudasta täytyy varata rinnakkaisuuden toteamiseen dynaamisesti sarjamuotoisesta koodista. Lisäksi raudan pitää yrittää kompensoida muistin viiveitä.

Yleensä ohjelmoijat koodaavat ohjelmia ajattelematta prosessorin muistihierarkiaa, ikään kuin käytössä olisi laaja, tasainen, yhtenäisen nopea muisti. Prosessorin pitää sen sijaan tulla toimeen fyysisten rajoitusten eli korkean latenssin ja rajoitetun kaistanleveyden kanssa liitännöissä ulkoiseen muistiin. Jotta toiminnallisille yksiköille saataisiin syötettyä dataa pitää prosessorin myös spekulatiivisesti hakea ennalta (pre-fetch) ulkoisesta muistista prosessorin välimuisteihin, jotta data olisi lähempänä laskentaa. Vaikka näitä tekniikoita on paranneltu vuosikymmenien ajan, niistä saatavien hyötyjen määrä on vuosien varrella merkittävästi vähentynyt.

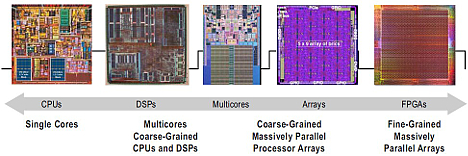

Kuva 1. Ohjelmoitavien ja rinnakkaisten tekniikoiden viimeaikaiset trendit.

Kun näiden kahden trendin tuomat hyödyt ovat vähentyneet perinteisissä prosessoriarkkitehtuureissa, on ohjelmoitavien laitteiden kirjo nopeasti kehittynyt, kuten kuvasta 1 näkyy. Painopiste on siirtymässä käskytason rinnakkaisuuden automaattisesta suorittamisesta ajonaikana siihen, että säietason rinnakkaisuus määritellään koodatessa. Tarjolle on tullut hyvin pitkälle rinnakkaisia moniydinprosessoreita, joissa on enemmän yksinkertaisia suorittimia ja laskentaan on varattu enemmän transistoreja kuin välimuistiin lukemiseen ja rinnakkaisuuden määrittämiseen. Nämä piirit vaihtelevat 2,4 tai 8 ytimen mikroprosessoreista grafiikkasuorittimiin, joissa sadat yksinkertaiset ytimet on optimoitu rinnakkaisen datan laskentaan. Korkean suorituskyvyn saavuttamiseksi näissä moniydinpiireissä ohjelmoijan on eksplisiittisesti koodattava sovelluksessa rinnakkaisena. Jokaiselle ytimelle pitää osoittaa tehtävä niin, että kaikki ytimet voivat yhdessä toteuttaa halutun laskentatehtävän. Juuri tätä FPGA-suunnittelijoiden pitää tehdä luodessaan korkean tason järjestelmäarkkitehtuureita.

OpenCL - alustariippumaton standardi

Tähän moniydinprosessorien vaatimien rinnakkaisten ohjelmien luomisen tarpeeseen kehitettiin OpenCL (Open Computing Language) -ohjelmointikieli tarkoituksena luoda alustariippumaton rinnakkaisen ohjelmoinnin standardi. OpenCL tuo mahdollisuuden kuvailla rinnakkaisia algoritmeja, joita voidaan toteuttaa FPGA-piireillä, paljon korkeammalla abstraktiotasolla kuin laitekuvauskielillä kuten VHDL tai Verilog. Vaikka tarjolla on useita korkean tason synteesityökaluja, joilla tämä korkean tason abstraktio saavutetaan, ne kaikki ovat kärsineet samasta perusongelmasta. Nämä työkalut yrittävät luoda sarjamuotoisesta C-ohjelmasta rinnakkaisen HDL-toteutuksen. Ongelma ei ole niinkään HDL-toteutus kuin säietason rinnakkaisuuden määritteleminen, jonka myötä FPGA-toteutus voisi saavuttaa paremman suorituskyvyn.

Kun FPGA on rinnakkaisuuden kirjon äärimmäisin esimerkki, epäonnistuminen maksimaalisen rinnakkaisuuden löytämisessä johtaa suurempiin vaikutuksiin kuin muissa piireissä. OpenCL-standardi ratkaisee monet näistä ongelmista antamalla suunnittelijan täsmällisesti määritellä ja kontrolloida rinnakkaisuutta. OpenCL-standardi vastaa luonnollisemmin FPGA-piirien pitkälle rinnakkaista luonnetta kuin C-kielessä kuvatut sarjamuotoiset ohjelmat.

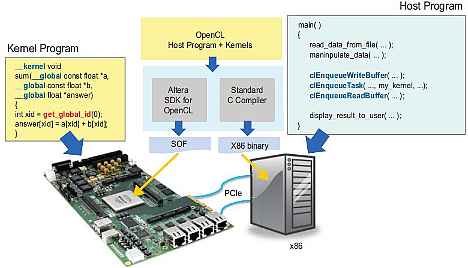

OpenCL-sovellukset koostuvat kahdesta osasta. OpenCL-isäntäohjelma on puhdas standardilla C/C++-kielellä kirjoitettu ohjelmistorutiini, joka toimii millä tahansa mikroprosessorilla. Tämä prosessori voi olla esimerkiksi ohjelmistopohjainen prosessori FPGA-piirillä, kovakoodattu ARM-prosessori tai ulkoinen x86-prosessori.

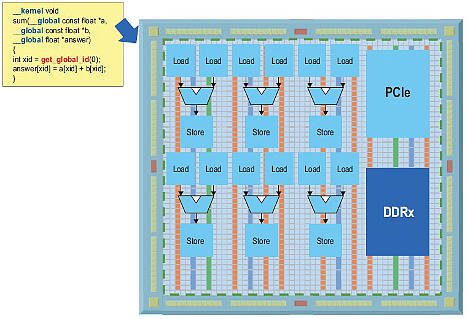

Jossakin vaiheessa tämän isäntärutiinin ajoa tulee todennäköisesti vastaan toiminto, joka on laskennallisesti vaativa ja joka voi hyötyä pitkälle rinnakkaisesti kiihdytyksestä rinnakkaisemmalla piirillä: CPU:lla, grafiikkaprosessorilla, FPGA-piirillä, jne. Tähän kiihdytettävään toimintoon viitataan OpenCL-ytimenä (kernel). Nämä ytimet kirjoitetaan standardilla C:llä, mutta niihin lisätään huomautuksia rakenteista, joilla yksilöidään rinnakkaisuus ja muistihierarkia. Kuvassa 2 näkyvä esimerkki suorittaa kahden lausekkeen - a ja b - vektorilisäyksen. Tulos kirjoitetaan takaisin lähtölausekkeena (output).

Rinnakkaiset säikeet operoivat vektorin kahta elementtiä. Tämän ansiosta tulos saadaan paljon nopeammin, kun sen laskentaa kiihdytetään piirillä, joka tarjoaa massiivisesti rinnakkaisuutta kuten esimerkiksi FPGA. Isäntäohjelmalla on pääsy standardeihin OpenCL-rajapintoihin, joiden kautta data voidaan siirtää FPGA-piirille. käynnistää kernel FPGA-piirillä ja välittää laskennan tulos takaisin.

Kuva 2. Esimerkki OpenCL-toteutuksesta FPGA-piirillä.

FPGA-piirillä kernel- eli ydintoiminnot voidaan muuntaa dedikoiduiksi ja tiukasti liukuhihnoitetuksi laitteistoksi, jotka ovat luonnostaan monisäikeisiä ja liukuhihnan rinnakkaisuutta hyödyntäviä. Jokainen näistä liukuhihnoista voidaan toistaa useita kertoja, jolloin päästään vielä suurempaan rinnakkaisuuteen kuin yhdellä liukuhihnalla.

OpenCL-standardin käytön edut FPGA-piirillä

Suunnittelujen luominen FPGA-piirille OpenCL-kuvauksella tuo useita etuja perinteiseen HDL-pohjaiseen metodologiaan verrattuna. Ohjelmoitavien laitteiden kehitys tapahtuu tyypillisesti niin, että ensin saadaan idea, sitten koodataan algoritmi korkean tason kielellä kuten C:llä, ja sen jälkeen luodaan käskysarja automaattisella kääntäjällä. Alteran OpenCL-ympäristössä OpenCL-sovelluksia voidaan toteuttaa FPGA:lla helposti. Tämä on esitetty kuvassa 3.

Kuva 3: Yleiskuva Alteran OpenCL-kehitysympäristöstä.

Tätä lähestymistapaa voidaan verrata perinteiseen FPGA-pohjaiseen suunnitteluun, joka edellyttää sitä, että suunnittelija luo jaksokohtaiset (cycle-by-cycle) laitteistokuvaukset raudasta, jolla algoritmi toteutetaan. Perinteinen vuo pitää sisällään datapolkujen luomisen, tilakoneen (state machine) näiden datapolkujen kontrollointiin, liitännän alemman tason IP-ytimiin järjestelmätyökaluilla, ja ajoitusongelmista huolehtimisen, koska ulkoiset liitännät tuovat rajoituksia, joihin täytyy mukautua. Alteran OpenCL-kehitysympäristö tekee kaikki nämä tehtävät automaattisesti suunnittelijan puolesta, joten suunnittelija voi keskittyä määrittelemään algoritmiaan sen sijaan että kuluttaisi aikaansa raudan yksityiskohtien viimeistelyyn. Tällä menetelmällä suunnittelija voi helposti viedä suunnittelunsa uusille FPGA-piireille, jotka tuovat paremman suorituskyvyn ja enemmän kapasiteettia, koska OpenCL-käännin muuntaan korkean tason kuvaukset liukuhihnoiksi, jotka hyödyntävät uutta FPGA-rakennetta.

OpenCL-standardin hyödyntäminen FPGA-piirillä voi tuoda merkittävästi paremman suorituskyvyn selvästi pienemmällä tehonkulutuksella, kuin mihin tämän hetken rauta-arkkitehtuureilla (CPU, GPU, jne.) päästään. Lisäksi OpenCL-standardia hyödyntävällä heterogeenisella FPGA-järjestelmällä (CPU + FPGA) on mahdollista viedä tuote markkinoille selvästi nopeammin kuin perinteisessä FPGA-suunnittelussa, jossa käytetään alemman tason laitekuvauskieliä kuten Verilogia tai VHDL:ää.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.