Useiden toisistaan riippumattomien kellosignaalien tuottaminen useita suorittimia sisältäviin FPGA- taiSoC-järjestelmiin tuo monimutkaisia haasteita laitteiden suunnittelijoille. Käyttäjän ohjelmoitava monilähtöinen kellogeneraattoripiiri tarjoaa tähän helpon ja kustannustehokkaan ratkaisun.

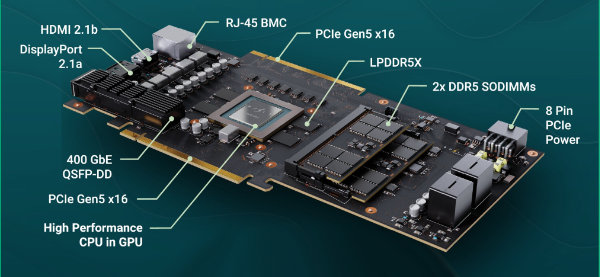

Nykyiset sulautetut järjestelmät ovat paljon monimutkaisempia ja kehittyneempiä kuin vielä muutama vuosi sitten. Piirisuunnitelma saattaa sisältää FPGA-logiikan lisäksi näytönohjaimena toimivan grafiikkaprosessorin (GPU) sekä useita liitäntöjä eri tarkoituksiin: video, USB, WiFi, nopea Ethernet ja ehkä myös ModBus- tai Fieldbus-liitäntä teollisuussovelluksia varten. Kukin näistä suorittimista ja alijärjestelmistä vaatii tyypiltään ja taajuudeltaan yksilöllisen kellosignaalin, joka on järjestelmän muista osista riippumaton. Suunnittelijan näkökulmasta tällainen järjestelmä, joka tuottaa useita erityyppisiä kellosignaaleja vaaditulla tarkkuudella ja jakaa ne omiin kohteisiinsa, tuo paljon haasteita, jotka liittyvät lukuisiin muihin suunnittelutyön osiin.

Ilmeinen ja suoraviivainen tapa tuottaa tarvittavat kellosignaalit vaikuttaa yksinkertaiselta: käytetään niin monta kellogeneraattoripiiriä kuin tarvitaan ja sijoitetaan niistä kukin piirilevylle lähelle omaa kohdettaan. Toinen suoraviivainen mahdollisuus on hyödyntää isäntäkellon ohjaamaa puumaista kellosignaalin jakelua. Näin voidaan ratkaista monikello-ongelma ainakin teoriassa, sillä kunkin kohteen yksilöllisiin vaatimuksiin räätälöity kellosignaali täyttää kyseisen lohkon tarpeet. Koska kukin kellolähde on sijoitettu lähelle omaa kohdettaan, kellosignaalin ylikuuluminen on vähäistä sekä kellojen kesken että niiden ja hyötysignaalien välillä. Näin saadaan myös kellosignaalien särö- ja värinätasot minimoitua.

Yhden kellopiirin käyttäminen kuhunkin kohteeseen vaikuttaa houkuttelevalta ratkaisulta, mutta se sisältää myös useita heikkouksia:

1. Suunniteltavan laitteen materiaalikustannuksiin (BOM) tulee välittömästi roima lisäys lukuisista eri kellogeneraattoripiireistä sekä niiden hankintaan ja hallintaan liittyvästä logistiikasta.

2. Ratkaisu vaatii myös merkittävästi lisää tilaa piirilevyltä, mikä on ongelmallista lähes kaikissa suunnittelutöissä.

3. Jos käytetään erillisiä yksilähtöisiä kellogeneraattoripiirejä eikä hyödynnetä jakelussa puumaista kellorakennetta, kukin kello tarvitsee myös oman kvartsikiteensä, mikä edelleen lisää sekä kustannuksia että levytilan tarvetta.

4. Puurakenteen käyttäminen kellosignaalien lopullisessa jakelussa kasvattaa sekin kustannuksia, levytilan tarvetta, kellosignaalin värinää ja virhetoimintojen mahdollisuuksia.

5. Useiden kellogeneraattoripiirien käyttäminen lisää myös koko laitteen tehonkulutusta.

6. Useiden kellopiirien käyttäminen vaikeuttaa lisäksi aiempien suunnitelmien uudelleenkäyttöä eri tuotteiden kesken valmistajan tuotantolinjalla, koska uudessa tuotteessa saatetaan soveltaa eri kellokomponentteja ja niiden erilaista sijoittelua piirilevylle.

Näiden tekijöiden tärkeys kussakin tilanteessa riippuu laaditusta piirisuunnitelmasta, sen painopistealueista ja mahdollisuuksista kompromisseihin. Päätös käyttää yhtä kellogeneraattoripiiriä ja kidettä aina jokaista erillistä kellosignaalia varten tuottaa lukuisia tahattomia seurauksia useita suorittimia sisältävissä järjestelmissä.

Vaihtoehtoinen tapa helpottaa

Suunnitteluun on tarjolla myös toisenlainen lähestymistapa, jonka avulla voidaan välttää erillisten kellogeneraattoripiirien käytöstä aiheutuvat haitat. Monilähtöinen ohjelmoitava kellogeneraattoripiiri tuottaa yhdestä kvartsikiteestä toisistaan riippumattomat lähtösignaalit, joilla voidaan korvata kaksi, neljä tai vieläkin useampia erillisiä kellosignaaleja. Näitä IC-piirejä on saatavissa laaja valikoima eri lähtövaihtoehdoin, konfiguraatioin ja taajuusaluein lukuisiin eri sovelluskohteisiin.

Monilähtöistä kellogeneraattoripiiriä valittaessa on tarkasteltava kriittisesti sen tarjoamia ominaisuuksia erilaisten kellokuormien tarpeisiin. Monissa piirisuunnitelmissa eri kohteiden kellokuormilla on erilaiset vaatimukset kellotaajuuden lisäksi jännitetasojen ja -muotojen, nousu- ja laskuaikojen maksimiarvojen sekä signaalin värinän suhteen. Monimutkaisen FPGA-piirin tai SoC-järjestelmäpiirin kellosignaalilla on paljon tiukemmat vaatimukset kuin esimerkiksi hitaalla tietoliikenneliitännällä samassa piirisuunnitelmassa, mutta suunnittelija haluaisi silti valita kellogeneraattoripiirin, joka voi täyttää kaikki eritasoiset vaatimukset.

Ohjelmoitavien kellogeneraattorien uusin sukupolvi suoriutuu näistä kovistakin vaatimuksista. Esimerkiksi Xilinxin FPGA-piiriperheet Virtex 6 & 7 sisältävät lähetin-vastaanottimia, joiden datanopeudet vaihtelevat välillä 480 Mb/s – 6,6 Gb/s sekä 2,488 Gb/s – 11,18 Gb/s, PCI Express -väylän raakadatan sekuntinopeudet yltävät enimmillään 5,0 gigabittiin linjaa kohti ja Ethernetin MAC-lohkot tukevat 10/100/1000 Mb/s linkkejä.

Näihin FPGA-piireihin perustuvien järjestelmien suunnittelutarpeisiin IDT on esitellyt ohjelmoitavien kellogeneraattorien VersaClock 6 -piiriperheen (kuva 1). Kellogeneraattoreihin on valittavissa 1-8 konfiguroitavaa lähtöä (LVDS tai LVPECL) ja 2-4 kertaohjelmoitavaa (OTP) konfiguraatiota valitusta piiristä riippuen. Kaikki kellogeneraattorit perustuvat murtojakoa (fractional output divider) hyödyntävään arkkitehtuuriin, joka tarjoaa maksimaalisen joustavuuden tuottamalla kaikki mahdolliset taajuudet välillä 1-350 MHz. Kellopiirien merkittävin piirre on erittäin alhainen vaihevärinä, jonka tehollisarvon taataan pysyvän kaikilla piireillä reilusti alle 500 femtosekunnin (0,5 ps).

Kuva 1: IDT:n VersaClock 6 –sarjan kellogeneraattoreissa on 2-8 konfiguroitavaa LVDS- tai LVPECL-lähtöä, joiden taajuudeksi käyttäjä voi ohjelmoida 1-350 MHz.

Sovellusesimerkki kuvastaa etuja

Hyvä esimerkki ohjelmoitavien monilähtöisten kellopiirien tuomista eduista on piirisuunnitelma, jonka täytyy tukea SMPTE-standardia. Myös nimellä 3G-SDI tunnetulla standardilla on erittäin tiukat vaatimukset ns. silmäkuviovärinän suhteen, kun mitataan 3 Gb/s nopeuteen yltävän SerDes-toiminnon (serializer-deserializer) suorituskykyä vaaditun bittivirhesuhteen (BER) saavuttamiseksi. SMPTE (Society of Motion Picture & Television Engineering) on maailmalaajuisesti tunnustettu standardointielin, jonka valvomat spesifikaatiot kattavat digitaali-TV:n datansiirron fyysisen kerroksen nopeat SDI-liitännät (Serial Data Interface).

Standardin tärkeimmät määrittelyt ovat:

- Ajoitusvärinä enintään 2,0 UI huipusta huippuun välillä 10 Hz - 100 kHz.

- Kohdistusvärinä enintään 0,3 UI huipusta huippuun välillä 100 kHz - 297 MHz, suositus 0,2 UI.

Yksikköväli UI tarkoittaa aikaväliä kahden vierekkäisen tilanmuutoksen välillä digitaalisignaalissa sekä vastaavasti kellosignaalissa.

Monien videolähetyksiin tarkoitettujen järjestelmien tarve tukea sekä NTSC- että PAL-normien mukaisia HDTV-standardeja lisää vielä suunnittelun teknisiä haasteita. Niihin pitää sijoittaa sekä 148,5 MHz että 148,5/(1,001) MHz referenssikellot. Lisäksi videolähetysjärjestelmissä on selvä trendi tukea myös VoIP-lähetyksiä (Video-over-IP), minkä saavuttamiseksi suunnitelman on tuettava myös 10 gigabitin Ethernetin fyysistä kerrosta (10GE PHY), joten mukaan tarvitaan myös 156,25 MHz referenssikello.

Xilinx 7 -sarjan FPGA-piirit valitaan usein SMPTE-yhteensopiviin suunnitelmiin niiden samalle sirulle integroitujen tehokkaiden GTX/GTH/GTP-lähetin-vastaanottimien ansiosta. Silmäkuvion värinää koskevien SMPTE 424 -määritysten täyttämiseksi Xilinx on asettanut piireille erittäin tiukat kellosignaalin vaihekohinan (dBc/Hz) vaatimukset SerDes-toiminnassa. Jos samoja lähetin-vastaanottimia käytetään myös 10 Gb/s SerDes-toimintaan, erittäin tiukat vaihekohinavaatimukset ovat jälleen kriittisen tärkeitä. Kokonaisluvuista riippumattomat kellotaajuudet (148,5 MHz, 148,351648 MHz ja 156,25 MHz) yhdessä erittäin tiukkojen vaihekohinavaatimusten kanssa tarkoittavat, että integroidun kelloratkaisun tarjoaminen on tärkeä osa suunnittelutehtävää.

IDT:llä on onneksi tarjota tähän tarkoitukseen erityinen UFT-piiri (Universal Frequency Translator). Tämä vaihelukittua silmukkaa (PLL) hyödyntävä piiri pystyy omatoimisesti syntesoimaan kaikki edellä mainitut kellosignaalit. UFT-piiriä voidaan hyödyntää korkealuokkaisena syntesaattorina, joka tarvitsee oheiskomponenttina vain tavallisen rinnakkaisresonanssimuodossa värähtelevän kvartsikiteen taajuusreferenssiksi. UFT-perheen piirit tukevat kutakin PLL-silmukkaa kohti yhtä tai kahta nastoin valittavaa konfiguraatiota, jotka voidaan esiladata piirin sisäiseen haihtumattomaan OTP-muistiin automaattista toimintaa varten, joka käynnistyy käyttöjännitteen kytkeytyessä. Vaihtoehtoisesti halutun taajuusmuunnoksen konfiguraatiot voidaan syöttää piirille I2C-sarjaväylän kautta.

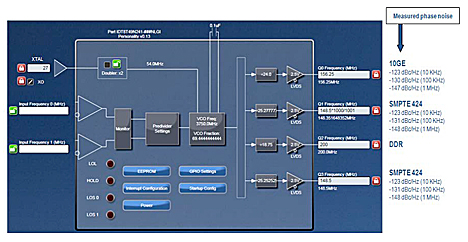

SMPTE 424 -määritysten mukaisessa piirisuunnitelmassa IDT:n UFT-perheen suorituskykyistä 8T49N241-piiriä voidaan käyttää nelilähtöisenä syntesaattorina, joten sen tarjoamat parannukset piirilevyalan hyödyntämiseen ja suunnittelun selkeyttämiseen ovat kiistattomia. UFT-piiriperheen kellogeneraattorit täyttävät kaikki Xilinx 7 -sarjan asettamat suorituskykyvaatimukset referenssikellolle tässä vaikeassa sovelluskohteessa.

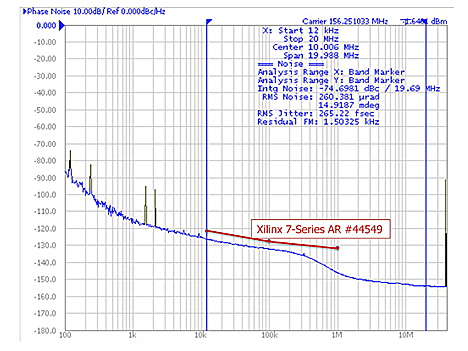

Kuva 2 esittää IDT:n UFT-kellopiirin tuottaman 156,25 MHz kellolähdön tyypillistä vaihekohina-käyrää. Käyrä kulkee selvästi alemmalla tasolla kuin Xilinx 7 -sarjan datalehdessä vaaditaan (Action Note AR# 44549).

Kuva 2: IDT:n UFT-kellopiirin tyypillinen vaihekohina 156,25 MHz taajuudella täyttää reilusti Xilinxin datalehden vaatimukset.

Jos suunnittelija valitsee ratkaisuksi yhden monilähtöisen kellogeneraattoripiirin, monet erillisten kellopiirien käyttöön liittyvät ongelmat häviävät tai muuttuvat paljon helpommiksi. Lisäksi kello-IC-piirin ohjelmoitavuus antaa mahdollisuuden hyödyntää samaa komponenttien sijoittelua useissa rinnakkaisissa tai edelleen parannelluissa laiteversioissa.

Suunnittelijan on pidettävä mielessä eräs tärkeä seikka soveltaessaan vain yhtä kellogeneraattoripiiriä. Kellopiirin sijoituspaikka ja kaikki piirilevyn johdinliuskat sen eri lähdöistä kuormakohteisiin on kyettävä mallintamaan ja simuloimaan. Tämä on tarpeen, jotta kellosignaalin eheys säilyy ja ylikuuluminen, kohina sekä värinä pysyvät riittävän alhaisella tasolla. Onneksi huippunopeita signaaleja ja niiden vaatimaa layout-rakennetta varten on nykyään saatavissa työkaluja, jotka mahdollistavat mallinnuksen ja simuloinnin. Niiden avulla voidaan samalla varmistaa koko suunnitelman suorituskyky myös kellottamattomien signaalien osalta.

Helppokäyttöisyys arvossaan

Monilähtöisen kellogeneraattorin kaltainen ohjelmoitava ja täysin konfiguroitava mikropiiri on käyttäjän kannalta turhauttava komponentti, ellei sen ohjelmointia tai konfigurointia voi suorittaa helposti. IDT:n kehittämä Timing Commander -ohjelmistoalusta antaa käyttäjälle mahdollisuuden konfiguroida ja ohjelmoida piirinsä intuitiivisella ja joustavalla tavalla graafisen käyttöliittymän (GUI) ansiosta.

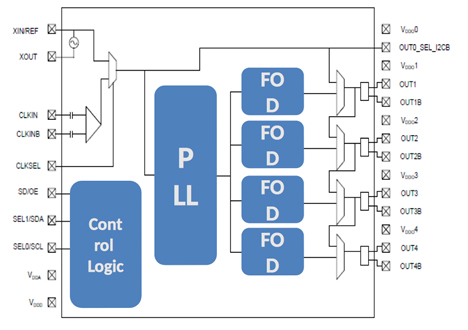

Kuva 3 esittää ruutukaappausta ohjelmiston käyttöliittymästä, kun sitä käytetään 8T49N241-piirin konfigurointiin nelilähtöiseksi syntesaattoriksi SMPTE 424 -sovellukseen. Piirin sisältämä murtojakoiseen takaisinkytkentään perustuva vaihelukittu silmukka (PLL) yhdessä kokonais- ja murtolukulähtöisten jakopiirien kanssa kykenee tuottamaan kaikki tarvittavat lähtötaajuudet synteesivirheen ollessa 0 ppb (parts per billion). Lisäksi 10GE- ja SMPTE-kellosignaaleista mitattu vaihekohina täyttää kaikki Xilinx 7 -piiriperheen vaatimukset.

Kuva 3: SMPTE-standardin mukaisen suunnitelman konfiguroinnissa IDT:n Timing Commander -ohjelmiston käyttöliittymä hyödyntää murtojakoiseen takaisinkytkentään perustuvaa vaihelukittua silmukkaa (PLL) yhdessä kokonais- ja murtolukulähtöisten jakopiirien kanssa tuottamaan kaikki tarvittavat lähtötaajuudet.

Monilähtöisen piirin uudelleenohjelmointiin voidaan tarvittaessa käyttää myös I2C-väyläohjelmointimuotoa ohittamaan OTP-muistiin esiladatut konfiguraatiot, jotka normaalisti otetaan käyttöön, kun käyttöjännite kytketään päälle. Lisäksi käyttäjät voivat ohjelmoida kunkin lähtöparin spektrinleveyttä järjestelmän tuottamien EMI/RFI-tasojen ja muiden häiriösignaalien vaimentamiseksi.

Käyttäjän mahdollisuus ohjelmointiin palvelee moniprosessorijärjestelmien suunnittelijoita monin eri tavoin ja poistaa lukuisia ongelmia, jotka liittyvät erillisten, itsenäisesti toimivien kellogeneraattoripiirien käyttöön. Ja kaikki tämä tarjotaan suorituskyvystä tinkimättä. Ohjelmoitavuus tukee erityyppisten kellokuormien tarpeita vain yhtä piiriä käyttäen, jolloin kysymykset tyyliin ”minkälainen kellosignaali tarvitaan minkäkin tyyppiselle kellokuormalle?” voidaan ratkaista. Taajuuden lisäksi voidaan räätälöidä myös muut kriittiset spesifikaatiot, jotka erottavat hinnaltaan, suorituskyvyltään ja hyötysuhteeltaan optimoidut suunnitelmat muista, liian moniin kompromisseihin ajautuneista piirisuunnitelmista.

Artikkelin on kirjoittanut IDT:n tuotelinjapäällikkö Baljit Chandhoke.

Lisätietoa

AN-815, "Understanding Jitter Units”

AN-827, "Application Relevance of Clock Jitter"

AN-840, "Jitter Specifications for Timing Signals"

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.