Erittäin nopeiden datansiirron laitteiden suunnittelu säilyy hyvin haasteellisena myös tulevaisuudessa. Hyödyntämällä joustavia ohjelmoitavia matriiseja, sirupohjaisia IP-lohkoja ja monipuolista suunnitteluohjelmistoa voidaan kehittäjien työtä kuitenkin merkittävästi helpottaa.

Erittäin nopeiden datansiirron laitteiden suunnittelu säilyy hyvin haasteellisena myös tulevaisuudessa. Hyödyntämällä joustavia ohjelmoitavia matriiseja, sirupohjaisia IP-lohkoja ja monipuolista suunnitteluohjelmistoa voidaan kehittäjien työtä kuitenkin merkittävästi helpottaa.

|

Artikkelin on kirjoittanut Craig Davis, joka toimii Intelillä ohjelmoitavien ratkaisujen tuotemarkkinoinnin päällikkönä. |

Huippunopea datansiirto etenee yhä lähemmäksi verkon reunaa. Viime aikoina sadan gigabitin Ethernet (100GE) on tyypillisesti ollut varattuna pääasiassa runkoverkon liikennettä varten, mutta moniytimisiin prosessoreihin ja virtualisointiin pohjautuvan kehitystyön ansiosta 100GE-laitteita sijoitetaan yhä useammin myös laitekaappien palvelinkorteille. Ja tämä kehitys näyttää vain jatkuvan.

Siirtonopeuden voimakkaan kasvun perustana on datansiirrossa käytettävien lähetin-vastaanottimien ripeästi kehittyvä tekniikka. 100G-, 200G- ja 400G-luokan optisia moduuleja tukevan yksittäisen lähetin-vastaanottimen on kyettävä siirtämään dataa 58 gigabitin sekuntinopeudella ja näköpiirissä ovat jo 112 Gb/s nopeuksilla toimivat versiot. Avain entistä suurempien datanopeuksien saavuttamiseen on optisen moduulin ja lähetin-vastaanottimen välinen liitäntä. Esimerkiksi 100GE-luokan järjestelmissä se on yleensä toteutettu käyttämällä CAUI-4-liitäntää (4 x 256 Gb/s).

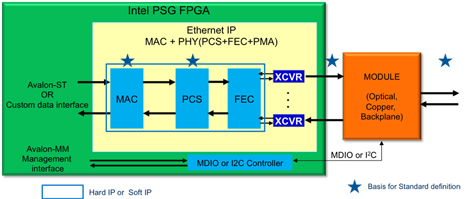

Kuten kuvasta 1 nähdään, Ethernet-datapolku hyödyntää useita toiminnallisia elementtejä. Lähetin-vastaanottimen lisäksi käytössä ovat FEC-korjauslohko (Forward Error Correction), fyysisen koodauksen alikerros PCS (PHY Coding Sublayer) sekä MAC-lohko (Media Access Control).

Kuva 1. Ethernet-datapolun rakenne.

Vaikka lähetin-vastaanotin on aina toteutukseltaan laitepohjainen, tukitoiminnot voidaan toteuttaa FPGA-matriisiin tallennettuina ohjelmallisina IP-lohkoina. Koska nopeudet edelleen kasvavat, näiden lohkojen toteutuksessa yleistyy kuitenkin sirupohjainen IP optimaalisen suorituskyky/tehosuhteen saavuttamiseksi.

Lähetin-vastaanottimen toteutus

Huippunopeisiin lähetin-vastaanottimiin ja niiden datapolkuihin pääseminen optimoinnin mahdollistavalla tavalla on kriittinen tekijä. Ohjelmoitavien matriisien luontainen konfiguroitavuus antaa tähän mahdollisuuden, kuten Intelin Stratix 10 -perheen FPGA-porttimatriisipiirit ja SoC-järjestelmäpiirit osoittavat.

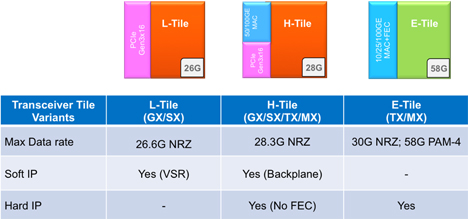

Stratix 10 -perheen piireissä lähetin-vastaanottimet on toteutettu erillisinä lohkoina, joita kutsutaan tiiliksi (Tile) ja jotka kytketään FPGA-matriisiin käyttäen EMIB-liitäntää (Embedded Multi-Die Interconnect Bridge). Tarvittavat Ethernet-toiminnot toteutetaan tuotteesta riippuen näissä tiilissä joko ohjelmistopohjaisina IP-lohkoina tai sirupohjaisina IP-lohkoina. Stratix 10 -perheen lähetin-vastaanottimien kolme tiilivaihtoehtoa ovat L-Tile, H-Tile ja E-Tile. Kuvassa 2 nähdään näiden kolmen vertailu maksiminopeuden sekä ohjelmallisen ja sirupohjaisen IP-toteutuksen suhteen.

Kuva 2. Stratix 10 -piiriperheen lohkotiilien vaihtoehdot vertailussa.

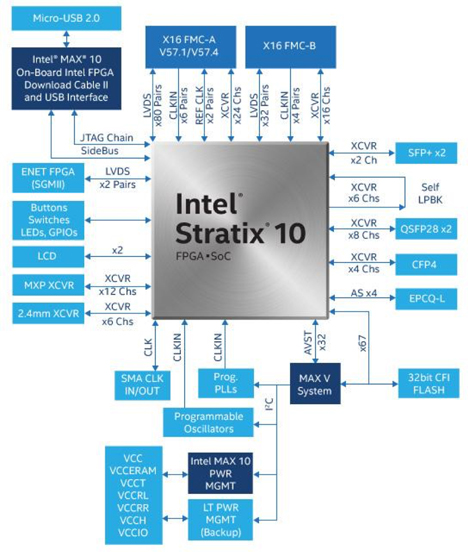

Lähetin-vastaanottimien ominaisuuksia ja suorituskykyä voidaan arvioida käyttämällä Stratix 10 -perheelle tarkoitettua kehityspakettia (Signal Integrity Development Kit). Sen avulla suunnitteluryhmät voivat luoda ja verifioida PRBS-malleja (Pseudo-Random Binary Sequence) hyödyntämällä suunnittelussa Quartus Prime Pro -ohjelmistoympäristöä (yhden vuoden lisenssi sisältyy evaluointikorttiin). Ohjelmiston avulla voidaan myös dynaamisesti muokata kunkin siirtokanavan differentiaalista lähtöjännitettä, esijännitteitä ja kanavientasauksen asetuksia optimaalisen suunnittelutuloksen saavuttamiseksi. Kuvassa 3 nähdään evaluointikortin lohkokaavio.

Quartus Prime Pro -ohjelmistoympäristön lisäksi kehityspaketti sisältää useita sovelluksia, jotka on tarkoitettu kehityskortin liittämiseen ja asetusten muokkaukseen. Niihin kuuluu muun muassa kellon hallintaan tarkoitettu Clock Control Application, jonka avulla suunnittelija voi asettaa käyttöön haluamansa kellolähteen ja -taajuuden Stratix 10 -kehityskorttia varten.

Kuva 3. Stratix 10 -kehityskortin lohkokaavio.

Monipuolinen paketti

Suunnittelijat voivat käyttää kehityskorttia ja -ohjelmistoa Stratix 10 FPGA -piiriin sulautettujen 100GE-ominaisuuksien laadun testaamiseen. Ohjelmisto tukee useita virheenkorjausmenetelmiä, joita ovat esimerkiksi BER-suhteen parantamiseen tarkoitettu RS-FEC, lähteviin Ethernet-kehyksiin lisättävä 32-bittinen CRC-sekvenssi kehysten tarkistamiseksi, johdanto-osan määritys sekä tuki Transceiver Toolkit -paketille (osa Quartus-ympäristöä).

Stratix 10 -piirin lisäksi kehityspaketti sisältää

- kuusi täysdupleksia lähetin-vastaanotinkanavaa 2,4 mm SMA-liittimin

- 24 täysdupleksia lähetin-vastaanotinkanavaa FMC+ A -liittimin

- 16 täysdupleksia lähetin-vastaanotinkanavaa FMC+ B -liittimin

- neljä täysdupleksia lähetin-vastaanotinkanavaa kuhunkin optiseen CFP4-liitäntään

- neljä täysdupleksia lähetin-vastaanotinkanavaa kuhunkin optiseen QSFP+ 0 ja QSFP+ 1 -liitäntään

- yksi lähetin-vastaanotinkanava sekä optiseen SFP+ 0 että SFP+ 1 -liitäntään

- neljä täysdupleksia lähetin-vastaanotinkanavaa kuhunkin tiheään MXP 0, MXP 1 ja MXP 2 -liittimeen

- FMC+ Loopback -tytärkortti testaukseen

Pakettiin kuuluvan DAC-kaapelin (Direct Attach Copper) avulla QSFP-kanavat voidaan kytkeä takaisinkytkentämuotoon (loopback) testausta ja evaluointia varten. Lisäksi pakettiin kuuluu AC-verkkolaite liitäntäkaapeleineen.

Asennuksen ja käyttöönoton jälkeen suunnittelijat voivat ladata valmiiksi käännetyn Quartus-ohjelmointitiedoston (SOF-tiedosto) lähetin-vastaanottimien testaamista ja evaluointia varten. Kun referenssisuunnitelma ajetaan Transceiver Toolkitin ollessa auki, näyttöön saadaan kahdeksan kanavaa, joista neljä on konfiguroitu lähetinmuotoon (TX) ja neljä vastaanotinkanaviksi (RX). DAC-kaapelin avulla neljä TX-kanavaa voidaan syöttää RX-kanaviin.

Transceiver Toolkitiin kuuluvan Transceiver Links -välilehden avaaminen näyttää kaikki kahdeksan kanavaa, ja samannimiset linkit, jotka päättyvät numeroihin 0, 1, 2 ja 3, kytketään yhteen. Ajamalla testimuoto PRBS 7 ja valitsemalla toimintamuodoksi Serial loopback – Internal loopback saadaan hyvä ensitesti, joka varmistaa, että lähetin-vastaanottimet toimivat. Nyt suunnittelijat voivat aloittaa testin, joka osoittaa, että bittivirhesuhde (BER) pysyy alhaisena jopa häviöllisen DAC-kaapelin kera.

Seuraava askel on kytkeä sarjamuotoinen takaisinkytkentä pois ja siirtyä testausmuotoon PRBS31 (oletusmuoto huippunopean siirron standardeja varten) sekä ajaa testi uudelleen läpi. Tässä vaiheessa tulisi näkyä, että BER-suhde muuttuu. Tämä voidaan nähdä ns. silmäkuviosta käyttäen Link Eye Viewer -toimintoa. Sen avulla suunnittelijat näkevät suoraan vaikutukset BER-suhteeseen ja silmäkuvion muotoon.

Linkin viritys ja optimointi voidaan nyt tehdä käyttämällä esikorostusta TX-kanavassa ja vaihtelemalla Adaptive Equalization -muotoja RX-kanavassa. Näitä ovat Adaptive CTLE, Adaptive VGA ja DFE, joita kaikkia voidaan hallita Transceiver Toolkitin avulla.

Lohkovariantit

Stratix 10 -perhe sisältää lohkovariantit L-Tile, H-Tile ja E-Tile. Näistä ensin mainittu sisältää 24 lähetin-vastaanotinkanavaa ja 8 sirulta sirulle -datansiirtoa 26,6 gigabitin sekuntinopeudella tukeva kanavaa. Maksiminopeus sirulta taustalevyyn on 12,5 Gb/s. L-tiili sisältää myös yhden PCIe Gen 3 x 16 -lohkon sirupohjaisena IP-lohkona.

H-Tile integroi niin ikään 24 lähetin-vastaanotinkanavaa, mutta laajentaa samalla sirupohjaisten IP-lohkojen valikoimaa kattamaan PCIe Gen 3 x 16 -lohkon SR-IOV-toiminnot ja 100GE MAC:n.

E-Tile puolestaan on lohkotiilien lippulaiva. Sen kussakin 24 lähetin-vastaanottimessa on itsenäinen PLL, toisin kuin L- ja H-tiilissä käytetyssä rakenteessa. E-Tile tarjoaa myös huippuluokan SERDES-suorituskyvyn 40 prosenttia alhaisemmalla tehonkulutuksella kuin H-tiili. Se myös tukee sekä NRZ- että PAM4-signalointia. Siihen kuuluu lisäksi kattava 100G/25G Ethernet IP, joka perustuu sirupohjaisiin FEC-lohkoihin. E-Tile tukee kahta eri FEC-tyyppiä, joista RS-FEC on tarkoitettu NRZ-signaloinnille ja KP-FEC PAM4-signaloinnille. Taustalevyn suorituskyky yltää 35 desibeliin 30 gigalla ja 30 desibeliin 58 gigalla.

Kaikkiaan Stratix 10 -perhe kattaa kolme eri FEC-tyyppiä. H-Tile tarjoaa sirupohjaisen Firecode-koodatun FEC-korjauksen, joka tukee 10 gigan datanopeuksia. E-lohkotiilen sirupohjainen RS-FEC puolestaan tukee NRZ-signaaleissa tapahtuvaa virheenkorjausta. E-tiileen on lisäksi integroitu KP-FEC-korjaus, joka tukee PAM4-signaaleja aina 58 gigaan asti.

Erillisten lähetin-vastaanottimien tiilet voidaan yhdistää ydinsirulla tuottamaan erilaisia Stratix 10 -pohjaisia aliperheitä tärkeisiin kohdesovelluksiin. Käytännössä tämä tarkoittaa, että suunnittelijalla on käytettävissään järjestelmä, joka voi sisältää neljä PCIe Gen 3 x 16 -liitäntää, joista kussakin on SR-IOV-tuki (4 PF/2K VF) ja neljä 100 GE MAC -lohkoa tai 20 RS-FEC-korjauksella varustettua 100GE MAC -lohkoa tai 120 RS-FEC-korjauksella varustettua 10/25GE MAC -lohkoa.

Stratix 10 -perhe tarjoaa monipuolisuudellaan ainutlaatuisia ominaisuuksia, joihin päästään kolmen erityyppisen tiiliversion avulla, jotka tukevat useita eri datanopeusluokkia ja tarjoavat välineet kanavientasaukseen. Tätä vielä täydentää erittäin suorituskykyinen sirupohjainen IP, joka soveltuu PCIe Gen 3:lle sekä 100GE-luokan RS+FEC/KP-FEC-järjestelmille.

Tämä suorituskyvyn ja laajennettavuuden ansiosta Stratix 10 -perhe yltää eturintamaan nopeiden järjestelmien suunnittelussa tarjoamalla käyttöön juuri sellaisia nopeuksia, joita asiakkaat haluavat nyt ja lähitulevaisuudessa.