FPGA-pohjaisten kiihdyttimien suunnittelu ja toteuttaminen ei tapahdu aivan käden käänteessä. Tarvitaan sovelluksen, infrastruktuurin ja RTL-suunnittelun kokonaisvaltaista yhteensovittamista. Kiihdytinsovelluksissa pääpaino on kiihdytinalgoritmeissa, jotka käsittävät useita monimutkaisia sekvenssejä. Onneksi kiihdyttimien integrointiin on nyt helpompi tie.

FPGA-pohjaisten kiihdyttimien suunnittelu ja toteuttaminen ei tapahdu aivan käden käänteessä. Tarvitaan sovelluksen, infrastruktuurin ja RTL-suunnittelun kokonaisvaltaista yhteensovittamista. Kiihdytinsovelluksissa pääpaino on kiihdytinalgoritmeissa, jotka käsittävät useita monimutkaisia sekvenssejä. Onneksi kiihdyttimien integrointiin on nyt helpompi tie.

| Artikkelin ovat kirjoittaneet Intelin Enno Luebbers, Song Liu ja Michael Chu. |

Suunnittelijat tavallisesti suunnittelevat kaikki tiedonsiirron yhteydet FPGA:n fyysisten ja loogisten kerrosten välillä sekä tarvittavan ohjelmiston prosessorille alusta lähtien ohjelmoimalla. Toinen vaihtoehto on käyttää valmiita IP-kirjastoja ohjelmoinnissa. Kumpikin tapa vaatii vielä paljon integrointia kiihdytettävien algoritmin osien RTL-suunnittelun lisäksi.

Kun yhä enemmän FPGA-piirejä käytetään pilvi- ja datakeskussovelluksissa koneoppimisessa, tarvetta on tehtävää helpottaville standardeille ja sovelluskehyksille. Open Programmable Acceleration Engine (OPAE) on yksi avoimista yhteisöistä, jonka pyrkimyksenä on yksinkertaistaa ja virtaviivaistaa FPGA-piirien integrointia kiihdytinsovelluksia varten.

OPAE koostuu useista ohjelmistokomponenteista, ajureista ja sovellusten käyttäjätilan API-liitännöistä. OPAE:n kevytversio edustaa yhtenäistä, kerrostettua rekonfiguroitavien kiihdyttimien ohjelmointiin perustuvaa mallia, joka tarjoaa yleisiä ja laajennettavissa olevia metodeja kiihdytinresurssien kehittämiseen, allokointiin, käyttöoikeuksiin ja hallintaan. Käyttöoikeudet ohjelmistopinoon on toteutettu eri kerroksissa testaamisen, kasvattamisen ja käyttämisen helpottamiseksi. Käyttäjän API-tasolla OPAE tarjoaa abstraktiot resurssien käyttöoikeuksien ja hallinnan yksinkertaistamista varten ilman merkittävää vaikutusta suorituskykyyn. Tämän lähestymistavan ansiosta järjestelmäintegraattorien, ohjelmistokehittäjien ja kiihdytinsuunnittelijoiden ei tarvitse tehdä perus-FPGA-komponenttien uudelleen sovitusta rekisterihakuja, jaettua muistia, synkronointia ja rekonfigurointia varten. OPAE:n avulla suunnittelija voi valita abstraktiotason ja ohjauksen järjestämällä sovellusliitännät kaikkialle ohjelmistopinoon.

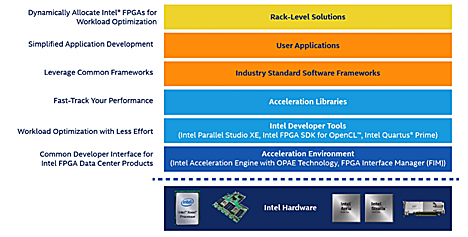

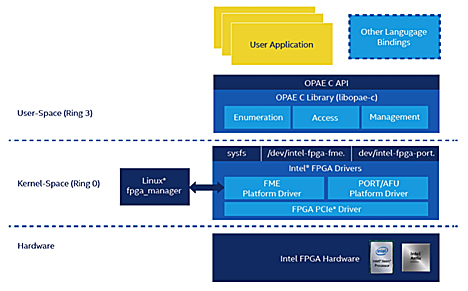

Kuvan 1 mukainen kokonaisvaltainen järjestelmäpino on lähestymistapa, jota tarvitaan aikaansaamaan kerrostettu yhteysmalli FPGA:n kiihdyttämisessä eri laitteissa, käyttöjärjestelmissä ja sovelluskohteissa. FPGA:n toteuttamisessa tarvitaan tällöin ajureita, käyttäjätilan API-liittymiä, sovelluskehyksiä ja sovelluskohtaisia kirjastoja.

Kuva 1. Intelin Xeon-palvelinprosessorin ja FPGA:n yhteydessä käytettävä kiihdytinpino.

Kiihdyttimen laitteistoresurssit, jotka koostuvat FPGA-piireistä, liitännöistä ja kehyslogiikasta, muodostavat alimman kerroksen ja ne on tavallisesti yhdistetty prosessoriin standardeilla järjestelmäväylillä osoitteen käännöslogiikkoineen ja välimuistihierarkioineen. OPAE:lla ei ole vaikutusta liitäntäteknologiaan tai topologiaan. Se kuitenkin edellyttää, että ohjelmoitava logiikka käyttää ohjelmistoilla toimivia datarakenteita laitteistokomponenttien ja resurssien tunnistamiseen ja tilastoimiseen. Rekonfiguroitavien laitteistoresurssien fyysinen yhteysliitäntä ei tavallisesti ole suoraan sovellusten käytettävissä.

Kuva 2. OPAE:n kerrokset ja komponentit.

Joukko ajureita on järjestelmän yhteysväylän yläpuolella ja ohjelmoitavat laitteistoresurssit kytkevät ja integroivat kiihdytinresurssit käyttöjärjestelmän laitteistohallintaan, näin ollen mahdollistaen perusyhteyskäytännöt käyttäjätilan sovelluksiin. Ajurikerroksen tärkeänä tehtävänä on varmistaa perusyhteyskäytäntöjen oikea toiminta järjestelmän integriteetin takaamiseksi, samoin kuin taustalla toimivien kriittisten hallintotehtävien kuten virheen-, tehon- ja lämmönhallinnan suorittaminen. Ajurin käyttäjän määriteltävissä olevien tilojen API on yhä käyttöjärjestelmästä ja laitteistosta riippuvainen.

Jotta laitteiden, alustojen ja käyttöjärjestelmien välisen siirrettävyyden edut saadaan käyttöön samalla kun voidaan tarkasti ohjata yksittäisiä resursseja, OPAE tarjoaa läpinäkyvällä käyttäjätilan kirjastolla (libopae-c) toteutetun C API -kerroksen, joka on liitettävissä laiteajurin API-rajapintaan alemman abstraktiotason kiihdytinresurssien toteuttamiseksi ja joka mahdollistaa näiden resurssien luetteloinnin, käyttöoikeuden ja hallinnan. Etenkin abstraktiomallin komponenttien tarjoaman ratkaisut ovat vielä jossain määrin FPGA-teknologiasta riippuvaisia, mutta niillä voidaan ilmaista halutun tasoisesti suuri joukko kiihdytinresursseja, alustoja ja käyttöalueita.

Integroimalla FPGA-ohjelmistopino standardoituihin ohjelmistokirjastoihin ja sovelluskehyksiin (esimerkiksi lineaarialgebran, syväoppimisen, salauksen, kompressoinnin ja muihin yleisiin toimintoihin) on mahdollista suoraan (läpinäkyvästi) kiihdyttää suurta määrää sovelluksia ja yksinkertaistaa toteutuksia erilaisissa käyttökohteissa, koska yksittäisten sovellusten ei tarvitse olla tekemisissä yksittäisten kiihdytinasteiden kanssa perustason tiedonsiirrosta puhumattakaan.

FPGA-pohjainen kiihdytinlaitteisto

OPAE-ajuri ja API-kirjastokerrokset koostetaan yksityiskohtaisista laitteistospesifikaatioista, joista saadaan tieto tiedonsiirtoyhteyksien määristä ja tyypeistä, hallintametodeista ja rekonfiguraatioiden käsittelytavoista. Pohjana olevan FPGA-laitteistoalustan on minimissään pystyttävä tarjoamaan infrastruktuuri näiden resurssien kehittämistä, allokointia ja yhteyskäytäntöjä varten.

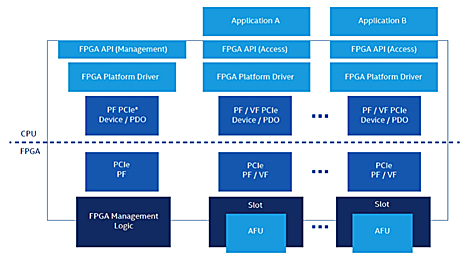

Kuva 3. FPGA-ajuri.

FPGA-ajuriarkkitehtuuri määrittelee yksittäiset alusta-ajurit hallintatoimintoihin, kuten rekonfiguraation ja kiihdyttimen yhteyskäytäntöihin. Edellinen liittyy FPGA-hallintalogiikkaan, kun taas jälkimmäinen hoitaa yleisten käytäntöjen mukaiset tiedonsiirtoyhteydet FPGA-lohkoon ohjelmoituun kiihdyttimeen. FPGA-ajurikerroksen tehtävänä on tasoittaa alla olevasta laitteistoarkkitehtuurista aiheutuvia vaihteluita, jolloin on mahdollista käyttää useampia eri liitäntäteknologioita ja säilyttää samalla järjestelmän integriteetti ja stabiilius. Joustavuuden lisäämiseksi FPGA-ajuri on segmentoitu pääajuriksi ja useiksi osa-ajureiksi. Pääajuri etsii ja tunnistaa FPGA-laitteita ja sen jälkeen aikaansaa vuorovaikutuksen yksittäisiin osa-ajureihin perustuen tunnistettuun laitteeseen liittyvään laiteosien toimintojen luetteloon.

FPGA:n API-liitäntä

Koodaajalle käytettävissä oleva API-liitäntä noudattaa kiihdytinresurssien oliopohjaista mallinnuskuviota siihen liittyvine toimintoineen. Toteutus on kuitenkin kirjoitettu C:llä, jotta minimoidaan piirikuvion vaatima ala ja sen vaikutus sovelluksiin.

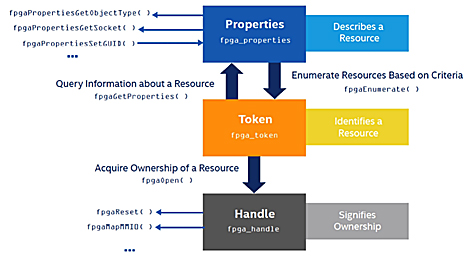

OPAE C API on mallinnettu kokoelmasta perusobjekteja, joilla kuvataan, identifioidaan ja referoidaan FPGA-resursseja. On syytä korostaa, että tässä kuvatut API:t muodostavat peruspaketin, joka on sovitettavissa useimpiin ohjelmistojärjestelmiin liitettäviin FPGA-kiihdyttimiin. API:n avulla voidaan myös mallintaa laitteisto- tai alustaspesifisiin laajennuksiin erityisiä kohdearkkitehtuurien erityisominaisuuksia. Esimerkkinä voidaan mainita alustaspesifinen API-laajennus, joka toimii pieniviiveisenä ilmoitusmekanismina Intelin Xeon-prosessorin yhtenäisen muistiväylän ja integroitujen FPGA-piirien välillä.

Kuva 4. OPAE C API:n olio- ja ohjauskaavio.

Kuvassa 4 esitetään tyypillinen API-perustaisten toimintojen etenemiskaavio sovelluksessa, joka haluaa käyttää ja saada käyttöoikeudet tiettyyn kiihdyttimeen. Aluksi sovellus luo ominaisuuksia kuvaavan olion, joka määrittelee etsittävän olion tunnuspiirteet ja joka siirretään fpgaEnumerate()-kutsuun sisältäen joukon symboleita, joilla identifioidaan yksittäiset resurssipyynnöt. Symbolin pitäminen hallussa ei merkitse siihen liittyvän resurssin omistamista. Symbolin valitsemisen jälkeen sovellus tekee kutsun fpgaOpen() hankkiakseen omistukseensa resurssin, joka puolestaan luovuttaa pidikkeenä toimivan kahvaosoittimensa. Tällä osoittimella voidaan kutsua yksittäisiä API-toimintoja ajantasaisesti ottamaan yhteyttä FPGA-kiihdyttimeen esimerkiksi kiihdyttimen uudelleen asettamista, ohjausrekisterien lukua ja kirjoitusta tai jaetun muistin allokointia varten. Lopulta fpgaClose() sammuttaa kahvaosoittimen ja purkaa resurssin omistuksen.

Sovelluskehyksen integrointi

Vaikka API:n tarjoamat perusresurssiabstraktiot helpottavat sovellusten tekoa erilaisille käyttöjärjestelmille ja alustoille, sovelluskehittäjä joutuu miettimään, miten resurssien käyttöoikeudet hoidetaan. Yksi lähestymistapa OPEA:a käytettäessä on integroida FPGA-kiihdytinresurssit lausekielisiin sovelluskehyksiin ja kirjastoihin. Tällä tavoin sovellusten ei tarvitse tietää kiihdytinresurssien yhteydenoton määrittelyjä ja tällöin kiihdytintoiminnot pysyvät läpinäkyvinä. Lausekielisten kirjastojen avulla saavutettava läpinäkyvyys FPGA-kiihdyttimissä tarjoaa etuja esimerkiksi kuvantunnistuksen, data-analytiikan ja datakompression tapaisissa sovelluskohteissa.

FPGA-sovellusten suunnittelu vaatii erikoisosaamista ja kykyä kohdata haasteita. OPAE:n avulla FPGA-pohjaisten kiihdytinratkaisujen kehitystyötä ja toteuttamista voidaan helpottaa merkittävästi. Tällöin yhä useampi suunnittelija voi keskittyä datakeskuksissa monimutkaisten datankäsittelysovellusten nopeuttamiseen.