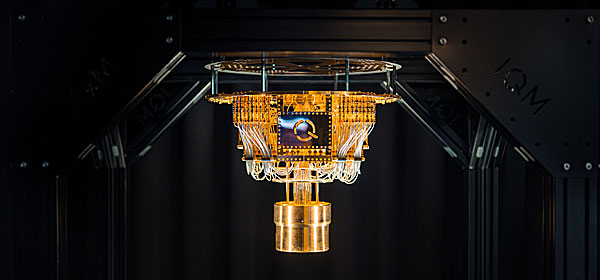

IC-suunnittelu kohtaa yhä vakavampia haasteita: piirit kehittyvät kohti 3D-arkkitehtuureja, chiplettejä ja ohjelmistopohjaisia järjestelmiä, mutta pätevistä suunnittelijoista ja verifioijista on huutava pula. Samanaikaisesti bugien löytäminen ennen valmistusta vaikeutuu, ja yhä useampi projekti myöhästyy tai epäonnistuu jo ensimmäisessä silikoni-iteraatiossa.

Siemens näkee tilanteen vakavuuden ja vastaa siihen uudella Questa One -verifiointialustallaan, joka yhdistää tekoälyn, automaation ja dataohjautuvan ajattelun. Sen tavoite on paitsi parantaa suunnittelun virheiden tunnistamista, myös kuroa umpeen ns. design gap -kuilua, joka tarkoittaa suunnitteluresurssien riittämättömyyttä yhä vaativampiin hankkeisiin.

- Pelkkä suorituskyky ei enää riitä. Tarvitaan syvempää yhteyttä suunnittelutyökalujen, testausmenetelmien ja tekoälyn välillä, sanoo Siemensin verifiointiyksikön johtaja Abhi Kolpekwar.

Questa One koostuu useista tekoälypohjaisista osakokonaisuuksista. Smart Regression ennustaa, mitkä testit todennäköisimmin epäonnistuvat, ja ajaa ne ensin. Property Assist käyttää generatiivista tekoälyä luodakseen formaaleja verifiointiominaisuuksia automaattisesti. Stimulus-Free Verification voi lyhentää vuorokauden mittaisen analyysin alle minuuttiin.

Lisäksi uusi simulaattori ja protokollapohjainen debugointi tekevät työstä nopeampaa ja vähemmän manuaalista.

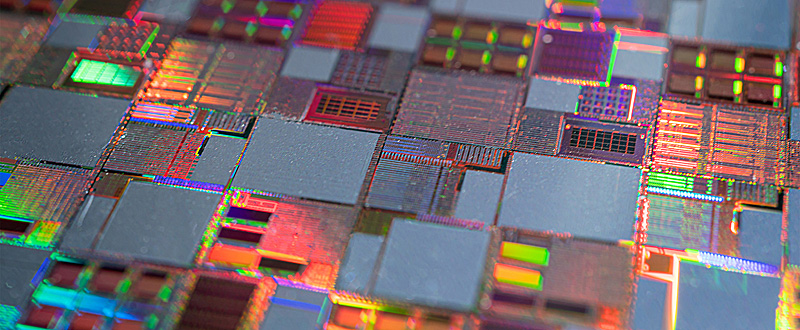

Käytännön hyötyjä on jo nähty: Arm, MediaTek ja Rambus ovat raportoineet huomattavia säästöjä ajassa ja kustannuksissa. Esimerkiksi MediaTekin mukaan AI-avusteinen verifiointi on säästänyt jopa viikkoja suunnitteluaikaa.

Siemensin julkistus käytännössä sanoo, ettei IC-suunnittelussa voi pysyä mukana ilman tekoälyä. Questa One on ensimmäinen kokonaisvaltainen ratkaisu, joka ei pelkästään tehosta olemassa olevia prosesseja, vaan se muuttaa koko tavan tehdä IC-suunnittelua.