Monessa raskasta laskentaa vaativassa sovelluksessa tarvitaan liukulukulaskentaa, mutta sen toteuttaminen ohjelmoitavalla FPGA-piirillä on tähän asti ollut kömpelöä ja aikaavievää. Altera sanoo mullistavansa markkinat uusilla kovakoodatuilla DSP-lohkoillaan, jotka tuovat liukulukulaskennan piireille helposti.

Mikäli kehittäjä on tarvinnut liukulukulaskentaa esimerkiksi tutka- tai lääketieteen sovelluksessaan, tällainen laskentayksikkö on aiemmin pitänyt FPGA-suunnittelussa kiinteän pilkun DSP-lohkoiksi. Tämä on ollut aikaa vievää prosessi, joka myös haaskaa satoja logiikkaelementtejä jokaista laskentayksikköä kohti.

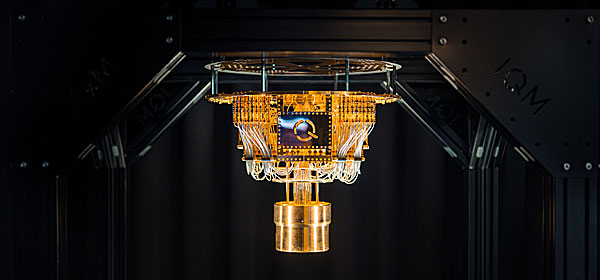

Alteran ratkaisussa jo toimituksissa oleviin Arria 10- ja Stratix 10 -piireihin on istutettu kovakoodattuja liukulukulohkoja jo olemassa olevien DSP-yksiköiden päälle. Ratkaisu on vaatinut esimerkiksi liitäntälogiikan muuttamista, mutta sen suorituskykyä lisäävä vaikutus on merkittävä.

Aleran mukaan uudet liukulukuyksiköt eivät käytännössä kasvata piirin piialaa eivätkä lisää tehonkulutusta. Suunnittelijan kannalta parasta on se, että liukuluyksiköt voidaan tuoda suunnitteluun suoraan esimerkiksi Simulink-mallina. Yhtiön arvion mukaan tämä lyhentää suunnittelijan työhön kuluvaa aikaa kuukausia, parhaimmillaan jopa 12 kuukautta.

Uudistuksen myötä Altera lupaa Arria 10 -piirien liukulukusuorituskyvyn nousevan aina 1,5 teraflopsiin. Stratix 10 -siruilla lukema nousee peräti 10 teraflopsiin. Käytännössä suunnittelija pääsee halutessaan eroon erillisistä DSP-prosessoreista ilman, että järjestelmän tehonkulutus kasvaa.

Altera tuo uudistetut DSP Builder -työkalut tarjolle vuoden jälkimmäisellä puoliskolla. 20 nanometrin prosessissa valmistetut Arria 10- ja Stratix 10 -piirit tulevat kaupallisesti tarjolle ensi vuoden aikana.