Altera on pian tuomassa tarjolle Intelin 14 nanometrin Tri-Gate-prosessissa valmistettuja ohjelmoitavia piirejä, jotka näyttävät testien perusteella tuovan sen kaksinkertaisen suorituskyvyn, jota Altera on asiakkailleen lupaillut. Prosessin lisäksi suorituskyvyn parantuminen perustuu uuteen Hyperflex-arkkitehtuuriin.

Tri-Gate on Intelin oma versio 3d-transistorirakenteesta, johon puolijohteissa ollaan kovaa vauhtia siirtymässä. Ero muiden valmistajien suosimaan FinFET-rakenteeseen ei ole kovin dramaattinen. Molemmissa perinteinen tasomainen portti korvataan hyvin ohuella piievällä tai -sillalla (fin), jonka kolmella eri puolella hallitaan virtoja erillisillä hiloilla.

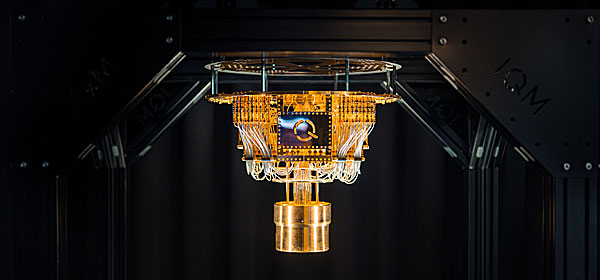

Altera kehuu nyt erityisesti uuden arkkitehtuurinsa tuomaa lisäystä suorituskykyyn. Ensimmäinen Hyperflex-piiriperhe on Stratix 10 ja testeissä asiakkaat ovat raportoineet erittäin hyviä lukemia.

Early access -ohjelmassa Alteran nykyisten 20 nanometrin piirien asiakkaiden suunnittelut on siirretty Intelin 14 nanometrin prosessiin. Tulosten mukaan suorituskyky on kasvanut vähintään kaksinkertaiseksi.

Esimerkiksi piirille toteutetut optiset kytkimet ovat toimineet yli 700 megahertsin kellolla, kun aiemmin nopeus oli 350 megahertsiä. Toinen hyvä esimerkki on gigabitin ethernet-liitäntä. Nykyisillä Stratix V -piireillä GbE-linkki toimii 1024-bitin levyisenä. Stratix 10 -siruilla 512-bittinen GbE-linkki toimii kaksinkertaisella nopeudella, joten sama suorituskyky saavutetaan selvästi pienemmällä piialueella.

Alteran mukaan Stratix 10 on markkinoiden suurin yhtenäinen FPGA-piiri, jolla on enimmilllään yli neljä miljoojnaa logiikkaelementtiä. Piirin suunnitteluun tarkoitettu ohjelmisto tulee jakeluun kesällä. Tuotteisiin uusi piiri ehtinee ensi vuoden alkupuolella.