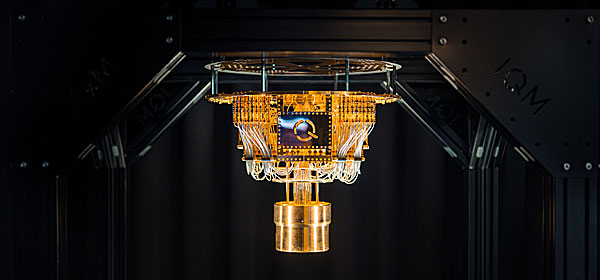

Piiritekniikan jokavuotinen IEDM-konferenssi on jälleen esitellyt uusia sirutekniikoita. Yksi mielenkiintoisimmista on Intelin demoama CMOS-piirien 3D-tekniikka. Siinä piitransistorin päälle oli pinottu galliumnitridi-transistori.

Intelin mukaan 3D-ratkaisun kaltaiset innovaatiot pitävät elossa sen tavoitteen, että prosessoripiirillä olisi vuonna 2030 jo biljoona eli tuhat miljardia transistoria. Tämä lienee hyvin hankalaa vain prosessigeometriaa kutistamalla, mutta 3D-rakenteilla täysin toteutettavissa.

Intelin 3D-rakenteen salaisuus on se, että transistorien virransyöttö siirretään hilan takapuolelle. Virtajohtimet saadaan myös vietyä transistorikerroksen läpi jo pari vuotta sitten esitellyn PowerVia-tekniikan ansiosta. Intelin mukaan tekniikka on tulossa kaupalliseen käyttöön jo ensi vuonna.

Intelin demossa transistorihilojen välinen etäisyys on 60 nanometriä. Piirit oli valmistettu 300-millisellä kiekolla ja ensimmäistä kertaa pii- ja GaN-transistorit oli toteutettu saman piirin sisällä, ei siis vain samassa kotelossa.

3D-rakenteita on käytetty muistipiireissä jo pitkään. Flash-siruissa on pinottu jopa yli 200 eri metallointikerrosta päälleikkäin. CPU-sirulla Intelin esittelemä piiri on kuitenkin toistaiseksi ensimmäinen ja ainoa.