Altera esitteli eilen uutta PLD-piiriperhettään, joka lanseerataan virallisesti vasta syyskuun lopulla. Samalla yhtiö kuitenkin kertoi, että Intelin 14 nanometrin Tri-Gate -prosessissa valmistetut FPGA-piirit tulevat myyntiin ensi vuonna.

Altera on pahimman FPGA-kilpailijansa tavoin käyttänyt tähän asti taiwanilaisen TSMC:n tuotantolinjoja ja -prosesseja. Uutta lippulaivamalliaan eli Stratix 10 -piirejä varten se kuitenkin kääntyi Intelin prosessiosaamisen puoleen.

Alteralla strategisesta markkinoinnista vastaava Shelly Davis kertoi eilen, että Intelin linjoilta tulee valmiita 14 nanometrin Stratix 10 -piirejä ensi vuoden puolivälissä. Käytännössä tämä tarkoittaa, että Alteran back end -valmistuksen - koteloinnin ja testaamisen -jälkeen asiakkaat saavat ensimmäiset 14 nanometrin FPGA-piirinsä käsiinsä ensi vuoden loppupuolella.

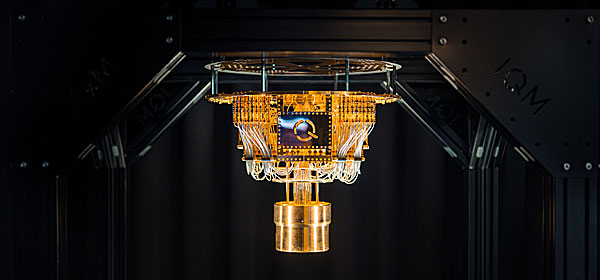

Tri-Gate on Intelin oma versio 3d-transistorirakenteesta, johon puolijohteissa ollaan kovaa vauhtia siirtymässä. Ero muiden valmistajien suosimaan FinFET-rakenteeseen ei ole kovin dramaattinen. Molemmissa perinteinen tasomainen portti korvataan hyvin ohuella piievällä tai -sillalla (fin), jonka kolmella eri puolella hallitaan virtoja erillisillä hiloilla.

Alteran mukaan Stratix 10 on markkinoiden suurin yhtenäinen FPGA-piiri, jolla on enimmillään yli neljä miljoonaa logiikkaelementtiä.