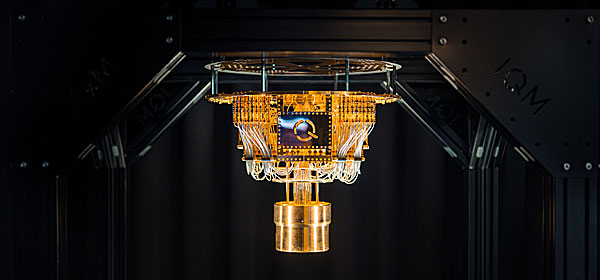

FPGA-valmistaja Altera on esitellyt järjestelmäpiirin, jossa samaan koteloon on ensimmäistä kertaa ahdettu tehokas ohjelmoitava piiri ja nopeaa DRAM-muistia. Ratkaisu tuo muistisuorituskykyä jopa 10-kertaisesti aiempiin ratkaisuihin verrattuna, joissa DRAM-piiri on erillisenä FPGA:n kyljessä.

Alteran SiP-kotelo (System-in-Package) yhdistää samojen kuorien sisään Stratix 10 -sarjan FPGA-piirin ja SK Hynixin erittäin nopean DRAM-piirin. Vastaavaa ratkaisua ei ole aiemmin nähty.

Sovelluskohteet löytyvät kaikista suurta muistinopeutta vaativista sovelluksista, kuten palvelinkeskuksista, yleisradiolaitteista, verkkolaitteita ja suurteholaskennan järjestelmistä, joilla analysoidaan esimerkiksi big dataa.

Altera on samalla ensimmäinen valmistaja, joka tuo pinotun 3D-muistin suoraan FPGA-piirin rinnalle. Yhtiö kertoo jo tekevänsä töitä yli 10 kumppanin kanssa, jotta uusi ratkaisu liitettäisiin osaksi niiden seuraavan sukupolven tuotteita.

Alteran piirillä FPGA-siru liitetään DRAM-muistiin Intelin kehittämän EMIB-väylän (Embedded Multi-Die Interconnect Bridge) välityksellä. Kyse on erittäin tiheästä siltapiiristä, joka yhdistää siruja saman kotelon sisällä. Liitännät kotelon sisällä jäävät lyhyiksi, joten ratkaisu siirtää dataa nopeasti ja pienemmällä tehonkulutuksella.

Stratix 10 on Alteran lippulaivapiiri, jolla hyödynnetään uutta reititysarkkitehtuuria. Sen, että dataväylää levennettäisiin, tehdään signaalipolusta nopeampi. Tätä arkkitehtuuria Altera kutsuu nimellä Hyperflex.

Idea on yksinkertainen. Datapolkua FPGA-matriisin sisällä liukuhihnoitetaan. Logiikkayksikköjen välille lisätään uusia rekisterejä, ns. hyperrekisterejä, joiden ansiosta signaalipolkujen pisin rekisterien välinen viive lyhenee merkittävästi. Tämän ansiosta matriisin kellotaajuutta voidaan nostaa ylemmäs.

Yhdistettynä SK Hynixin nopeaan DRAM-piiriin samassa SiP-kotelossa Hyperflex-prakenne tuottaa ohjelmoitavan piirin, jonka suorituskyky on aivan eri tasolla kuin mihin FPGA-piireissä on aiemmin totuttu.