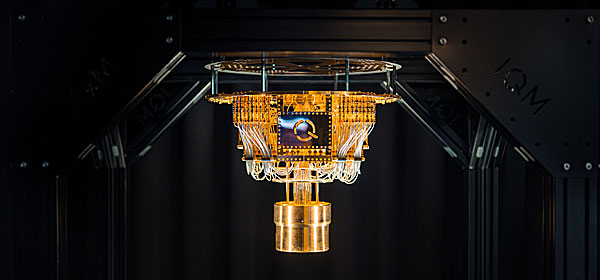

FPGA-piireillä on yhä enemmän sulautettuja prosessoreja. Ne ovat kuitenkin pääosin lisensoitavia ARM- tai Power-prosessoreita. Microsemi on nyt esitellyt ensimmäistä kertaa avoimeen arkkitehtuuriin perustuvan prosessoriytimen, joka voidaan integroida osaksi FPGA-piiriä.

Kyse on RISC-V-ytimestä, joka voidan istuttaa osaksi Microsemin Igloo2-, SmartFusion2- ja RTG4-sarjojen FPGA-piirejä. RISC-V ei oikeastaan ole prosessoriydin, vaan avoimeen koodiin perustuvat RISC-käskykanta..

RISC-V suunniteltiin alusta asti käytettäväksi erilaisia moderneissa laitteissa pilvipalvelimista älypuhelimiin ja pienimpiin sulautettuihin laitteisiin. Muihin käskykantoihin verrattuna RISC-V on täysin vapaasti käytettävissä laitevalmistajan tarpeisiin.

Microsemi tarjoaa ytimen RTL-koodia vapaaseen käyttöön. Tämän ansiosta ytimen luotettavuus ja tietoturva on suunnittelijan omissa käsissä.

Microsemi on kehittänyt RV32IM-ytimen yhdessä SiFive-yrityksen kanssa. Suunnittelua Microsemi tukee kattavalla Libero-työkalupaketilla, jolla Microsemin muutkin FPGA-piirit suunnitellaan.

Microsemi uskoo, että avoin prosessoriydin houkuttaa erityisesti turvallisuus- ja tietoturvasovelluksissa, koska ytimen RTL-koodi on vapaasti tarkistettavissa. Suljettuun arkkitehtuuriin perustuvissa prosessoreissa sama ei ole mahdollista.

Lisätietoja Microsemin uutuudesta löytyy yhtiön verkkosivuilta.