![]() Tekoälyä tuodaan nyt vauhdilla mikro-ohjaimiin. Ajan myötä kaikista päätelaitteiden ML-sovelluksiin tarkoitetuista mikro-ohjaimista tulee hybridilaitteita, joissa yhdistyvät CPU ja NPU. Tämä kehitys on väistämätöntä.

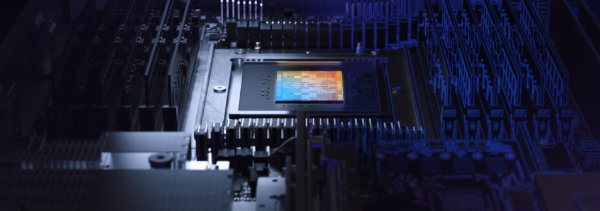

Tekoälyä tuodaan nyt vauhdilla mikro-ohjaimiin. Ajan myötä kaikista päätelaitteiden ML-sovelluksiin tarkoitetuista mikro-ohjaimista tulee hybridilaitteita, joissa yhdistyvät CPU ja NPU. Tämä kehitys on väistämätöntä.

|

Artikkelin on kirjoittanut Alif Semiconductorin markkinointijohtaja Mark Rootz. |

Perinteisille mikro-ohjaimille, jotka suorittavat sulautettuja ohjaustoimintoja ilman sisäistä tekoälylaskentaa, tulee aina olemaan kysyntää. Mutta nopeasti kasvava tarve suorittaa tekoälytoimintoja päätelaitteessa tulee yhä enenevässä määrin määrittämään mikro-ohjainten vaatimukset uusien suunnittelujen osalta, kuten kuvassa 1 esitetään makrotasolla.

MCU-markkinoiden taistelu tullaan yhä useammin voittamaan niiden toimesta, jotka kykenevät integroimaan neuroverkko- eli NPU-prosessorin ominaisuudet tiiviisti perinteisten mikro-ohjaintoimintojen kanssa. Mikro-ohjainten valmistajan valitsema arkkitehtuuri tälle uudelle hybridimuotoiselle CPU/NPU-laitteelle vaikuttaa merkittävästi laitevalmistajien tuotesuunnitteluun – suorituskykyyn ja vasteaikoihin, virrankulutukseen sekä tuotekehitystiimien tuottavuuteen.

Kaikki tämä vaikuttaa loppukäyttäjien tyytyväisyyteen: he odottavat sujuvaa ja hyödyllistä toiminnallisuutta ilman havaittavaa viivettä kohtuuhintaisissa tuotteissa, kuten puettavissa laitteissa, kuulokojeissa, kuntoilu- ja terveydenseurantalaitteissa, älykameroissa ja peleissä – entistä vähemmällä riippuvuudella pilvipalveluista.

Suunnittelijat, joiden tehtävänä on valita tekoälyä tukeva mikro-ohjain, tukeutuvat luonnollisesti suorituskykyvertailuihin ja muuhun tekniseen dataan – mutta he hyötyvät myös siitä, että kurkistavat konepellin alle ja tarkastelevat, miten NPU on integroitu perinteisen sulautetun ohjaimen rakenteeseen.

Kuva 1. Tekoälyä tukevan mikro-ohjaimen olennaiset komponentit.

Mikro-ohjainkisa uusille urille

Kilpailevien neuroverkkototeutusten vertailu mikro-ohjaimissa ei ole vielä noussut julkiseen keskusteluun. Tämä johtuu siitä yksinkertaisesta syystä, että vain harvat valmistajat ovat aidosti vastanneet markkinoiden tarpeeseen tehokkaasta koneoppimiskyvykkyydestä (ML) päätelaitteiden IoT-sovelluksissa. Suurimmat mikro-ohjainvalmistajat ovat enimmäkseen tyytyneet parantamaan nykyisiä tuoteperheitään lisäämällä ML-ominaisuuksia ohjelmistokehityspaketteihinsa (SDK), pitäen kuitenkin vanhan sukupolven piiri-IP:n pääosin ennallaan.

Tämä IP perustuu lähes aina vanhempiin Arm:n Cortex-M-suoritinarkkitehtuureihin ML-kuormien käsittelyssä, ja harvinaisissa tapauksissa käytetään omaa neuroverkkokäytinprosessoria. Lisäksi käytössä on perinteisiä sisäisiä muistiratkaisuja, jotka ovat alimitoitettuja, liiallisesti jaettuja ja sijoitettu epäoptimaalisesti suhteessa neuroverkkoprosessointiin, mikä estää ML-päätelmien eli inferenssien suorittamisen halutulla nopeudella ja virrankulutuksella. Kun joudutaan turvautumaan piirien ulkopuoliseen muistiin, järjestelmän kustannukset, koko ja virrankulutus kasvavat, samalla kun tietoturvan taso heikkenee.

Tämä tilanne tulee muuttumaan. Käytännön kokemus osoittaa mikro-ohjainten käyttäjille, että neuroverkkotoiminnot eivät sovi hyvin perinteisten mikro-ohjainten ohjauskeskeisten RISC-suorittimien rakenteeseen. Pysyäkseen virrankulutusrajojen sisällä ja täyttääkseen suorituskykyvaatimukset, päätelaitteisiin suunnatun mikro-ohjaimen on sisällettävä NPU-laitteisto, joka on optimoitu kertolasku- ja yhteenlaskuoperaatioita (MAC) varten – nämä ovat hermoverkkosovellusten perusta – ja sen on oltava yhdistetty erittäin suurikaistaiseen muistiin.

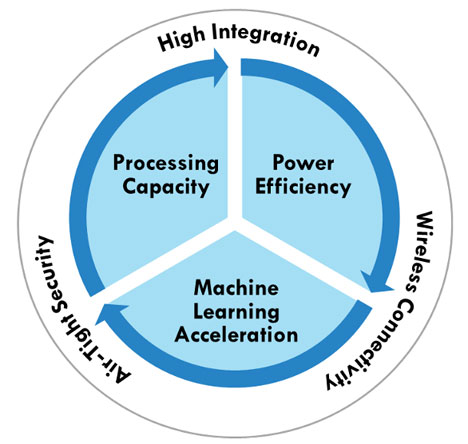

Taulukko kuvassa 2 havainnollistaa tätä asiaa. Alif Semiconductorin Ensemble-mikro-ohjainperhe hyödyntää nykyaikaista Cortex-M55-suoritinydintä, joka sisältää Single Instruction-Multiple Data (SIMD) -vektoriprosessointilaajennuksen nimeltään Helium, ja siihen on yhdistetty Ethos-U55 NPU -yhteisprosessori. Itse asiassa monissa Ensemble-mikro-ohjaimissa käytetään kahta Cortex-M55 CPU + Ethos-U55 NPU -paria, mutta tästä lisää myöhemmin.

Tässä nähdään mittaustuloksia yhdestä koneoppimispäätelmästä neljällä eri koulutetulla ML-mallilla, jotka suorittavat tehtäviä kuten avainsanojen tunnistus, objektien havaitseminen, kuvien luokittelu ja puheentunnistus Ensemble-ohjainpiirillä. Vasemmalta oikealle siirryttäessä vihreä alue osoittaa, milloin ML-mallin kuormaa suoritetaan hyödyntäen kaikkea käytettävissä olevaa laitteistokiihdytystä – eli Ethos-U55 NPU:ta yhdessä Cortex-M55-suorittimen kanssa, käyttäen sen SIMD-vektorikäskysarjaa.

Keltainen alue esittää samat mittaustulokset uudelleen, mutta ilman Ethos-U55 NPU:n apua. Sininen alue puolestaan näyttää tulokset, kun suoritus on täysin prosessoripohjaista – eli ilman minkäänlaista laitteistokiihdytystä, pelkästään CPU:n varassa.

Lopuksi suhteelliset suorituskykyparannukset on esitetty oikealla. Vihreä alue korostaa suorituskyvyn kasvua, joka saavutetaan käyttämällä kaikkia saatavilla olevia kiihdytyksiä verrattuna CPU:hun, joka käyttää vain SIMD:tä. Keltainen alue osoittaa suorituskyvyn parannuksen, jonka SIMD-käskyjä hyödyntävä CPU tuo verrattuna pelkkään CPU:hun ilman SIMD:tä. Sininen alue puolestaan näyttää suorituskyvyn kasvun, joka saavutetaan täyden laitteistokiihdytyksen avulla verrattuna tilanteeseen, jossa ei ole lainkaan kiihdytystä.

Kuva 2: Suorituskykytestit osoittavat NPU:n käytön ylivoimaisen suorituskyvyn ja tehokkuuden parannuksen yleisten ML-kuormien kiihdyttämisessä (klikkaa suuremmaksi, viitteet artikkelin lopussa).

Mitä näistä vertailuista voidaan oppia?

- Siniset alueet – Sulautettu CPU yksinään kamppailee merkityksellisten ML-kuormien kanssa, koska erittäin rinnakkaisista ML-verkoista johdetut päätelmät täytyy suorittaa sarjallisesti, mikä vie paljon aikaa ja kuluttaa runsaasti energiaa. Cortex-M55 on yksi parhaista sulautetuista suoritinarkkitehtuureista ja tarjoaa jo itsessään noin viisinkertaisen suorituskyvyn ML-tehtävissä verrattuna aiempiin Cortex-M-sukupolviin. Mutta vaikka Cortex-M55 on näin hyvä, katso oikealla olevan sinisen alueen vaikuttavaa suorituskykyparannusta – täyden kiihdytyksen käyttö tarjoaa jopa kahden kertaluvun (100-kertaisen) suorituskykyedun verrattuna pelkkään CPU:hun.

Ja kun otetaan huomioon, että Cortex-M55 tarjoaa jo noin viisinkertaisen suorituskyvyn verrattuna muihin laajasti käytettyihin Cortex-M-arkkitehtuureihin, voidaan nämä parannukset usein kertoa vielä uudelleen viidellä. Esimerkiksi puheentunnistuksessa tämä tarkoittaa noin 800 kertaa nopeampaa suoritusta ja 400 kertaa pienempää energiankulutusta per päätelmä!

- Keltaiset alueet. SIMD-pohjaisten vektorilaskentaominaisuuksien tuominen mikro-ohjainalueelle tarjoaa merkittäviä parannuksia suorituskykyyn ja virrankulutukseen verrattuna pelkkään CPU:hun, koska se mahdollistaa rinnakkaisemman käsittelyn. Helium- vektorilaajennus tuotiin tälle alueelle Cortex-M55-suorittimen myötä, osana Armv8.1-M-arkkitehtuuria.

- Vihreät alueet. Tässä erillinen NPU-yhteisprosessori todella loistaa. ML-kuorma jaetaan kääntäjän toimesta NPU:n ja CPU:n välillä, ja tyypillisesti jopa 95 % tai enemmän ML-kuormasta kohdistuu NPU:lle – riippuen käytetystä mallista. NPU suorittaa päätelmät erittäin nopeasti ja energiatehokkaasti toteuttamalla MAC-operaatiot laitteistotasolla erittäin rinnakkaisesti. Tärkeänä lisähyötynä CPU voi NPU:n työskentelyn aikana siirtyä lepotilaan säästääkseen energiaa tai hoitaa muita tehtäviä.

Ajan myötä kaikista päätelaitteiden ML-sovelluksiin tarkoitetuista mikro-ohjaimista tulee hybridilaitteita, joissa yhdistyvät CPU ja NPU. Tämä kehitys on yhtä väistämätöntä kuin muut perustavanlaatuiset trendit mikro-ohjainmaailmassa viime vuosikymmenten aikana – kuten siirtyminen flash-muistiin pohjautuviin mikro-ohjaimiin ja USB-yhteyden integrointi lähes jokaiseen mikro-ohjaimeen.

Uusia vaihtoehtoja kehittäjille MCU-arkkitehtuurien arviointiin

Tällöin kysymykseksi nousee, miten MCU-valmistajien arkkitehtuuriset valinnat liittyen neuroverkkokyvykkyyden integrointiin vaikuttavat OEM-valmistajien kehitystiimeihin?

Alifilla on perustamisestaan vuonna 2019 lähtien keskittynyt kehittämään tuotteita, jotka vastaavat koneoppimislaskennan kasvavaan tarpeeseen verkon päätepisteissä. Itse asiassa Alif oli ensimmäinen MCU-valmistaja, joka toi markkinoille skaalautuvan ohjain- ja langattomien MCU-piirien tuoteperheen, joka yhdistää Cortex-M-suorittimen ja Arm Ethos-U -neuroverkkoyksikön (NPU).

Tässä ovat kolme tärkeintä näkökulmaa hybridimallisessa CPU/NPU -arkkitehtuurissa, joihin OEM-kehittäjien tulisi kokemuksemme mukaan kiinnittää huomiota valitessaan MCU:ta verkon reunalla toimiviin ML-sovelluksiin.

1. Nopea, vähän virtaa kuluttava ML-päättely riippuu muistityypistä ja -topologiasta

OEM-valmistajat tulevat monissa tapauksissa toteuttamaan koneoppimista päätelaitteessa, koska sovellus vaatii käyttäjän kannalta välittömältä tuntuvan vasteen. Lisäksi suurin osa näistä tuotteista on kannettavia ja langattomia, joten pitkä akun käyttöikä on erittäin tärkeää.

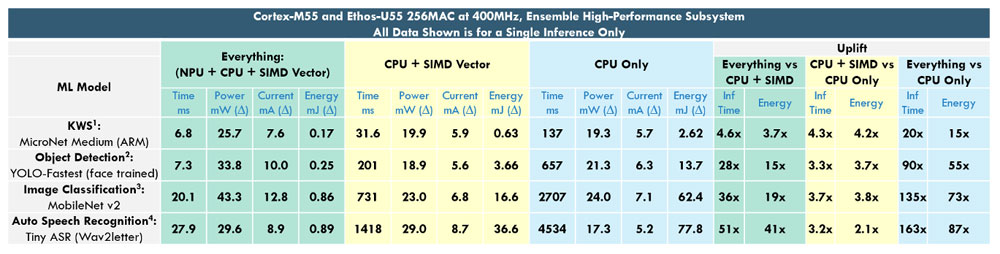

Kuvasta 2 nähtiin, että parannettu laskentakyky on avainasemassa korkean suorituskyvyn ja energiatehokkuuden saavuttamisessa, mutta ilman optimoitua muistijärjestelmää tulokset eivät vastaa odotuksia.

Yksinkertaistettu näkymä Ensemble MCU:n muistirakenteesta on esitetty kuvassa 3. Yläosa edustaa reaaliaikaista osaa, jossa erittäin nopea TCM-muisti (Tightly Coupled Memory) on liitetty CPU- ja NPU-ytimiin. Nopeaa (pienen viiveen) päättelyä varten näiden TCM-SRAM-muistien täytyy olla riittävän suuria ML-mallin tensorialueen säilyttämiseen.

Kaavion alaosa näyttää muut järjestelmän muistit, jotka on jaettu eri puolille ja liitetty toisiinsa yhteisen nopean väylän kautta. Suuri SRAM-muisti tarvitaan esimerkiksi anturidatan, kuten kameran tai mikrofonien syötteen tallentamiseen, ja suuri haihtumaton muisti sisältää ML-mallin itsensä sekä sovelluskoodin. Kun suuret sirun sisäiset muistit jaetaan tällä tavoin liikenteen ruuhkien minimoimiseksi, mahdollistetaan samanaikaiset muistitoiminnot, pullonkaulat vähenevät, muistien vasteaika lyhenee ja virrankulutus pysyy yhteensopivana pienen akun kanssa.

On tärkeää muistaa, että sulautetuissa ML-järjestelmissä suuri osa päättelyyn kuluvasta energiasta kuluu datan siirtämiseen paikasta toiseen. Järjestelmissä, joissa on liian pienet tai huonosti suunnitellut muistirakenteet, energian kulutus pelkkään datan liikuttamiseen voi ylittää sen, mitä CPU ja NPU kuluttavat varsinaiseen laskentaan. Lisäksi, jos ylimääräinen data tai koodi joudutaan tallentamaan ulkoiseen muistiin, energiankulutus voi kasvaa jopa kymmenkertaiseksi — ja samalla altistaa kriittisen sovelluskoodin ja ML-mallin immateriaalioikeudet mahdolliselle tietoturvaloukkaukselle.

Kuva 3. Emsemble-ohjaimen sisäinen muistitopologia.

2. Akun keston maksimointi

Alif tunnisti varhain, että paikallisen koneoppimiskyvykkyyden käyttö päätelaitteissa tulee kasvamaan räjähdysmäisesti lähitulevaisuudessa. Samalla näiden tuotteiden fyysinen koko tulee pienentymään nopeasti, erityisesti puettavissa laitteissa. Esimerkkejä tekoälyllä varustetuista puettavista laitteista, joiden markkinakysynnän odotetaan kasvavan merkittävästi, ovat älylasit, älysormukset ja kuulolaitteet. Kaikki nämä tarvitsevat virtalähteeksi yhä pienempiä akkuja.

Alifin lähestymistapa akun keston pidentämiseksi sisälsi useita keinoja. Tässä kaksi esimerkkiä:

- Järjestelmän osiointi siten, että matalatehoinen osa sirusta voi olla jatkuvasti päällä. Tämä jatkuvasti aktiivinen osa tarjoaa riittävän laskentatehon, jotta se voi valikoivasti herättää korkeamman suorituskyvyn osan sirusta suorittamaan raskaampia tehtäviä, minkä jälkeen palataan taas lepotilaan.

- Virranhallintajärjestelmä kytkee päälle vain ne sirun osat, joita tarvitaan, ja sammuttaa ne, kun niitä ei tarvita.

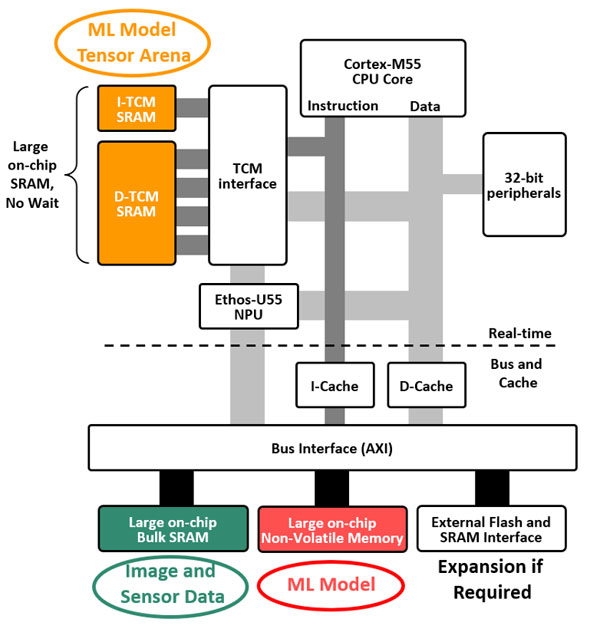

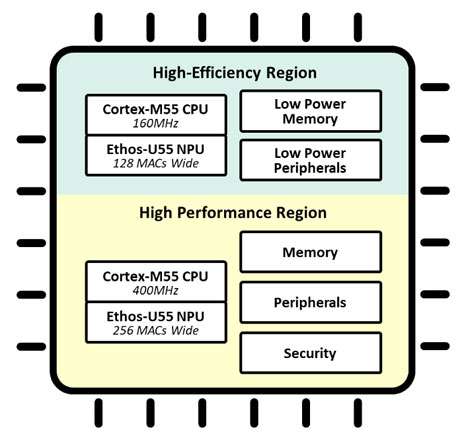

Monissa Ensemble MCU-piireissä on kaksi Cortex-M55 + Ethos-U55 -ydinparia, kuten kuvassa 4:

- Toinen pari sijaitsee sirun High-Efficiency (korkean energiatehokkuuden) alueella, joka on rakennettu matalavuotoisista transistoreista ja voi olla jatkuvasti päällä toimien jopa 160 MHz taajuudella.

- Toinen pari sijaitsee High-Performance (korkean suorituskyvyn) alueella ja toimii jopa 400 MHz taajuudella.

Tämän tuoman edun voi kuvitella seuraavan esimerkin avulla: älykäs kamera skannaa jatkuvasti huonetta matalalla kuvataajuudella hyödyntäen energiatehokkaita ytimiä luokitellakseen merkitykselliset tapahtumat (esimerkiksi ihmisen kaatumisen tai tietyn eleen). Tämä laukaisee suorituskykyiset ytimet suorittamaan kehittyneempiä tehtäviä, kuten henkilöiden tunnistamisen, poistumisteiden esteiden tarkistuksen tai avun hälyttämisen.

Tässä tapauksessa kamera voi valvoa älykkäästi, tuottaa vähemmän vääriä hälytyksiä ja pidentää akun käyttöikää. Samanlaista kahta CPU+NPU-ydinten paria voidaan yhtä hyvin soveltaa myös äänien, puheiden, sanojen, optisesti tunnistetun (OCR) tekstin, värähtelyjen ja monien muiden anturidatojen luokitteluun eri sovelluksissa.

Kuva 4: Ensemble E3 MCU -lohkokuvio, joka esittää sirun korkean energiatehokkuuden ja korkean suorituskyvyn alueet.

Kaikki Ensemble-ohjaimet hyödyntävät myös Alifin aiPM-teknologiaa eli autonomisen älykkään tehonhallinnan (autonomous intelligent Power Management) teknologiaa, jonka avulla sirun jopa 12 erillistä virtatoimialuetta voidaan hallita reaaliaikaisesti tarpeen ja sovelluksen käyttötapauksen mukaan. Vain ne toimialueet, jotka suorittavat aktiivisesti tehtäviä (esimerkiksi tietyt prosessoriytimet, muistit tai oheislaitteet) pidetään käynnissä, kun taas muut pysyvät pois päältä. Tämä tapahtuu ohjelmistokehittäjän näkökulmasta täysin läpinäkyvästi.

3. Kehittäjien tuottavuuden parantaminen

Monille reaaliaikaisen sulautetun ohjauksen parissa työskenteleville insinööreille tekoälyjärjestelmät ovat vieras alue, joka vaatii uudenlaista lähestymistapaa ohjelmistokehitykseen. Kehitysympäristön ei kuitenkaan tarvitse olla yhtä vieras.

Sulautettujen järjestelmien maailmassa on vakiinnuttu käyttämään Arm Cortex-M -arkkitehtuuria ohjaukseen, ja nyt myös Armin Ethos-NPU:t liittyvät tähän vakiintuneeseen ekosysteemiin hyödyntäen sen tuttuja ja toimiviksi todettuja etuja. Sulautettujen NPU-moottorien kentällä on kuitenkin tarjolla runsaasti muitakin vaihtoehtoja IP-toimittajilta, ja jotkut tunnetut MCU-valmistajat kehittävät myös omia, räätälöityjä NPU-ratkaisujaan.

Kaikki nämä muut vaihtoehdot vievät kuitenkin NPU:n pois Armin ekosysteemistä, jossa sulautetut ohjaustoiminnot kehitetään. Tämä tekee Ethos-NPU:sta paremman valinnan monille käyttäjille, koska se mahdollistaa tekoälytoimintojen kehittämisen samassa tutussa MCU-ympäristössä kuin ohjaustoiminnotkin.

Ensemble-ohjaimella Ethos-NPU toimii käytännössä älykkäänä oheislaitteena Cortex-M55-suorittimelle, johon se on tiiviisti liitetty ja jonka kanssa se jakaa TCM-muistiresurssit, joita Cortex-ydin hallinnoi. Tämä tarkoittaa, että kehittäjän ei tarvitse huolehtia laitteistoresurssien jaosta. Armin kääntäjä jakaa koneoppimistehtävät automaattisesti NPU:n ja CPU:n välillä ilman, että kehittäjän tarvitsee antaa erityisiä ohjeita resurssien kohdentamisesta.

Lisäetuna Ethos-NPU:n käytössä on se, että Arm vastaa sen ylläpidosta, mikä takaa, että se on aina ajan tasalla ja tukee uusimpia versioita siitä ML-kehityskehyksestä, jota kehittäjä haluaa käyttää – esimerkiksi TensorFlow Litea. Armin tuki Ethos-NPU:lle varmistaa, ettei kehittäjän tarvitse rajoittaa valintaansa ML-kehitysalustoissa.

Uudet arkkitehtuurit uusiin sovellusvaatimuksiin

Vaikka näkökulmia on monia, tämä artikkeli käsittelee kolmea tärkeintä perustaa, joiden varaan kilpailu ML:ää tukevien MCU-piirien tarjoamisesta näyttää rakentuvan. Alif tuli markkinoille varhain tarjotakseen MCU-piirejä, joissa on vahvat koneoppimiskyvyt päätepisteisiin. Samalla se ei unohtanut turvallisuutta, oikeaa oheislaitteiden ja liitäntöjen yhdistelmää, langatonta yhteyttä sekä laajaa valikoimaa skaalautuvia ja yhteensopivia laitteita. Nämä kattavat kaiken yhdestä RTOS:ää käyttävästä suorittimesta aina neliytimisiin laitteisiin, jotka tukevat myös Linux-käyttöjärjestelmää.

Se, mitä Alif on oppinut ollessaan edelläkävijä hybridimallisten Cortex-M / Ethos -MCU-piirien kehittämisessä, voi auttaa OEM-kehittäjiä määrittämään, millaisia ominaisuuksia ja toimintoja heidän valitsemansa MCU:n tulisi sisältää, kun tekoäly ja koneoppiminen nousevat sovellusvaatimusten kärkeen.

Alif jatkaa alan eturintamassa esittelemällä ensimmäiset MCU-piirit, joissa käytetään Armin seuraavan sukupolven Ethos-U85 NPU:ta, joka tukee transformer-pohjaisia ML-malleja generatiivisen tekoälyn sovelluksissa päätepisteessä.

Jo tänään kehittäjät voivat tutustua Ensemble-tuoteperheeseen osoitteessa www.alifsemi.com, ja aloittaa kehitystyön Ensemble Application Kitin avulla. Paketti sisältää Ensemble E7 -fuusioprosessorin, kameran, mikrofoneja, liikeanturin ja värinäytön.

Kuva. 5. Alif Ensemble kehityspaketti (AK-E7-AIML).

Kuvan 2 viitteet

1) KWS: From ARM MicroNets paper. Quantized int8, trained on ‘Google Speech Commands’ dataset. Model footprint: 154KB MRAM, 28KB SRAM

2) Object Detection: 192x192 grayscale resolution & color. Quantized int8, trained on ‘WIDER FACE’ dataset. Model footprint: 431KB MRAM, 433KB SRAM

3) Image Classification: 224x224 24bit resolution % color. Quantized int8, trained on ‘ImageNet’ dataset. Model footprint: 3,552KB MRAM, 1,47KB SRAM

4) ASR: Tiny Wav2letter Pruned slotted into ARM's ML demo app, running the ASR use case. MRAM=2346.06KB (greatly Vela optimized from 3903.43KB), SRAM=1197.20KB