Autoteollisuuden siirtymä kohti ohjelmistopohjaisia ajoneuvoja (SDV) kasvattaa järjestelmien laskentavaatimuksia nopeasti. Renesasin mukaan 3 nanometrin prosessisolmu tuo mukanaan uusia teknisiä rajoja, jotka eivät enää ratkea perinteisellä yhdelle piisirulle rakennetulla SoC-arkkitehtuurilla.

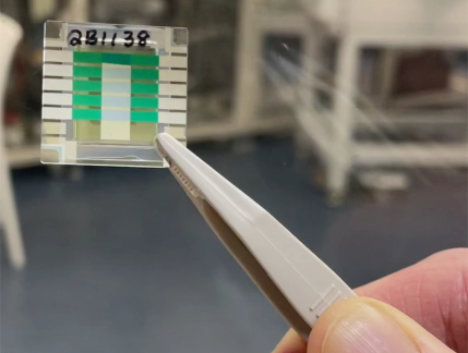

Yhtiö esitteli ISSCC 2026 -konferenssissa teknologioita, joilla se vastaa monidomainpohjaisten ECU-yksiköiden kasvavaan suorituskyky-, turvallisuus- ja energiatehokkuuspaineeseen. Keskeinen ratkaisu on sirpaleisiin (chiplet) perustuva arkkitehtuuri. Sen sijaan että kaikki toiminnot integroidaan yhteen suureen piisiruun, kokonaisuus jaetaan useaan pienempään sirpaleeseen, jotka liitetään toisiinsa UCIe-rajapinnalla.

Tämä tuo kaksi etua: Parempi valmistussaanto 3 nm -luokassa ja skaalautuvuus eri suorituskykytasoihin. Renesasin mukaan haaste ei kuitenkaan ole pelkkä liitäntätekniikka. Turvallisuuskriittisessä autoympäristössä sirpaleiden välinen tiedonsiirto on kyettävä eristämään siten, että eri sovellukset eivät häiritse toisiaan.

Yhtiö on kehittänyt mekanismin, jossa resurssit tunnistetaan RegionID-tunnisteilla ja eristys säilyy myös sirpaleiden välillä. Tavoitteena on täyttää ASIL D -tason vaatimukset ja niin sanottu FFI-periaate (Freedom from Interference), jossa yksikään ohjelmisto- tai laitekomponentti ei saa häiritä muita, saavutetaan koko piirin tasolla.

Kun transistoritiheys kasvaa, myös virrantiheys nousee. Suuritehoisissa autojen järjestelmäpiireissä tämä näkyy ongelmina virransyötössä (IR drop) ja lämpökuormana. Renesas kertoo jakaneensa sirun yli 90 virtadomainiin ja käyttävänsä kaksivaiheista tehonkytkentää, jolla jännitehäviötä voidaan pienentää noin 13 prosenttia. Yhtiö korostaa, että energiatehokkuus ja turvallisuus on ratkaistava samanaikaisesti. Pelkkä laskentatehon kasvattaminen ei riitä.

SDV-arkkitehtuuri nojaa yhä raskaampiin neuroverkkoihin. Renesasin mukaan NPU-lohkojen pinta-ala on kasvanut noin 1,5-kertaiseksi sukupolvesta toiseen. 3 nanometrin siruissa tämä aiheuttaa kelloviiveongelmia. Ratkaisuna on kellogeneraattorien hajauttaminen alilohkotasolle, jotta viiveet pysyvät hallinnassa.