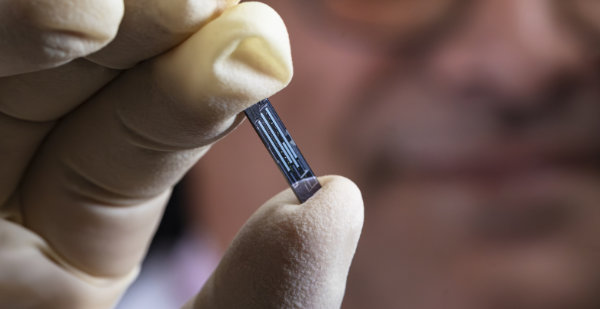

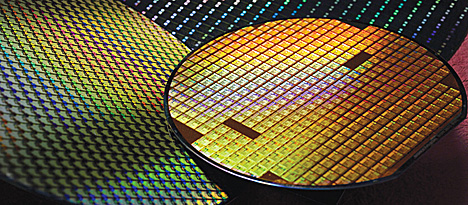

Taiwanilainen TSMC tunnetaan monien edistyneimpien puolijohdesirujen sopimusvalmistajana. Tällä hetkellä volyymituotantoon ovat siirtymässä 3 nanometrin prosessissa valmistetut piirit. Vuonna 2025 edessä ovat ensimmäiset isot sarjat N2-prosessissa, jossa viivanleveys on enää kaksi nanometriä.

TSMC:n 2 nanometrin prosessi perustuu nanolevy-tekniikkaan (nanosheet technology). Tämä viittaa transistorirakenteeseen, jota on kutsuttu nimellä GAA eli gate-all-around. GAA-rakenteen tärkein idea on se, että siinä hila ympäröi kanavaa kokonaan.

Nanolevytransistorin suorituskyky on ylittänyt 80 prosenttia TSMC:n aiemmin ilmoittamista teknologiatavoitteista. Transistorien kytkentänopeus on siis odotettua parempi samalla kun niiden energiatehokkuus on parempi (alhaisempi Vmin) Prosessi sopii siis erinomaisesti energiatehokkaaseen laskemiseen.

N2-prosessia on jo kokeiltu Arm A715 -suorittimen kanssa. Tämän hetken N3E-prosessiin (energiatehokas 3 nanaometrin prosessi) sillä päästiin 30 % nopeuden lisäykseen samalla teholla. Toisin päin: samaan suorituskykyyn päästään kolmanneksen pienemmällä tehonkulutuksella.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.