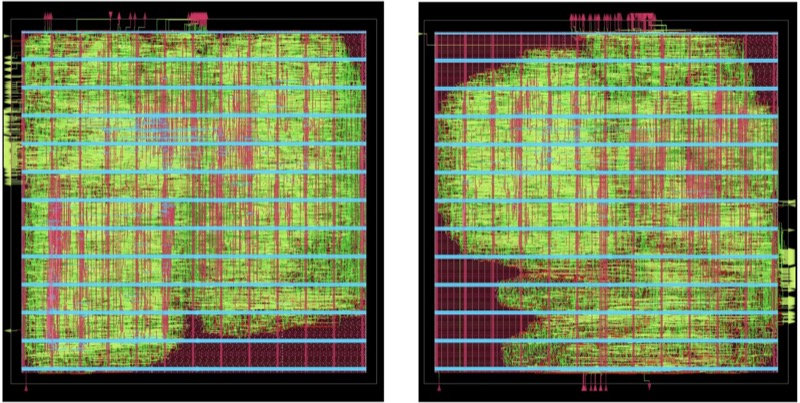

Diplomi-insinööri Sakari Lahden tuore väitöskirjatutkimus Tampereen yliopistosta osoittaa, että korkean tason synteesi voi jopa puolittaa piirien kehitystyöhön kuluvan ajan verrattuna manuaaliseen RTL-suunnitteluun. Erityisesti FPGA-pohjaisissa projekteissa HLS tarjoaa huomattavan tuottavuushyödyn, kun aikaa vievät mikroarkkitehtuurin yksityiskohdat jätetään automaattisen työkalun huoleksi.

Digitaalisten piirien suunnittelu kohtaa jatkuvasti kasvavia vaatimuksia, kun sovellusten kompleksisuus lisääntyy Mooren lain mukaisesti. Suunnittelun tuottavuuden kasvattamiseksi alan huomio on kohdistunut korkean tason synteesiin (High-Level Synthesis, HLS), jossa perinteisten laitekuvauskielten kuten Verilogin ja VHDL:n sijaan käytetään korkeamman tason ohjelmointikieliä, erityisesti C++:aa. HLS mahdollistaa järjestelmien nopeamman toteutuksen, koska suunnittelija voi keskittyä toimintalogiikkaan ilman, että hänen täytyy käsin määritellä kellosyklejä ja datapolkuja.

Kaikkiin sovelluksiin C++ ja HLS eivät kuitenkaan sovi täydellisesti. Kun tavoitteena on äärimmäinen suorituskyky, pienin mahdollinen logiikkapinta-ala tai minimitehonkulutus, käsin kirjoitettu Verilog- tai VHDL-koodi tarjoaa edelleen parhaat tulokset. Väitöskirjan mukaan HLS-suunnittelu tarvitsee usein sovelluksen uudelleenrakentamista laitteistokeskeiseen muotoon ja syvää ymmärrystä FPGA- ja ASIC-arkkitehtuurien erityispiirteistä, jotta tulosten laatu vastaa manuaalista RTL-toteutusta.

C++-lähtöisessä HLS-suunnittelussa ohjelmoijan on esimerkiksi kiinnitettävä huomiota tarkkaan datatyyppien valintaan, muistihierarkian optimointiin sekä silmukkarakenteiden pipeliningiin ja unrollingiin. Ilman näitä optimointeja automaattisesti generoitava laitteistokuvaukset voivat jäädä tehottomiksi. Tämä tarkoittaa, että pelkkä ohjelmointitaito ei riitä, vaan HLS-suunnittelijalta vaaditaan myös laitteistospesifistä osaamista.

Silti HLS ja C++ tarjoavat erityisen houkuttelevan vaihtoehdon nopeille kehityssykleille ja prototyypinrakennukselle, missä aikataulut ovat tiukkoja ja täydellinen resurssitehokkuus ei ole kriittinen. Kehitystrendi on selvä: yhä useampi projekti hyödyntää korkean tason synteesiä, ja työkalujen jatkuva parantuminen lupaa kaventaa HLS:n ja manuaalisen RTL:n välistä suorituskykyeroa tulevaisuudessa. Parhaassa tapauksessa HLS voi tulevaisuudessa syrjäyttää perinteiset suunnittelutavat yhä useammissa sovelluksissa.

Lahden tietotekniikan alaan kuuluva väitöskirja Evaluation of the State of High-level Synthesis: A Hardware Engineer’s Perspective tarkastetaan julkisesti Tampereen yliopiston informaatioteknologian ja viestinnän tiedekunnassa perjantaina 09.05.2025.