EDA-talo Cadence Design Systems on tuonut formaalin verifioinnin piirisuunnittelujen RTL-koodin parantamiseen. Nyt JasperGold-työkalulla onnistuu bugien etsintä myös RTL-koodista. Tuloksena on laadukkaampi koodi, vähemmän muutoksia koodiin loppuvaiheessa ja merkittävä ajansäästö IP-suunnittelussa.

RTL-koodista on aiemmin etsitty bugeja esimerkiksi manuaalisilla testeillä ja staattisilla säännöntarkistuksilla. Tämä tarkistus on tyypillisesti tehty liian myöhään suunnitteluvuossa. Löytyneet bugit tarkoittavat RTL-koodin uudelleentyöstämistä ja projektin hidastumista.

Cadencen tavoitteena on nyt löytää RTL-koodin virheet mahdollisimman aikaisessa vaiheessa suunnitteluvuota. Verifiointi-insinöörille pitää saada koodia, joka on valmiimpaa. Se onnistuu vain formaalisilla menetelmillä tarkistamalla.

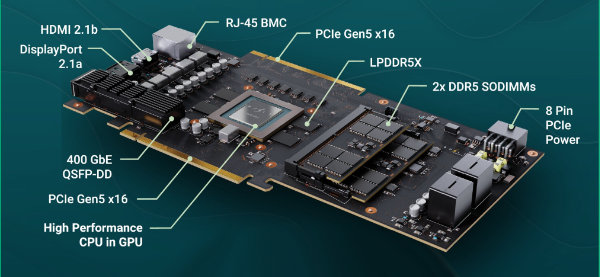

Formaalia verifointia on aiemmin tehty lähinnä verkkolistalle eli ennen RTL-synteesiä. JasperGoldiin lisätyt uudet sovellukset (appsit: SuperLint ja CDC, Clock Domain Crossing) tarkistavat RTL-koodin virheiden varalta automaattisesti formaalien sääntöjen mukaisesti. Tuloksena on koodia, joka on valmista simuloitavaksi vaikkapa Cadencen Xcelium-simulaattorissa.

Testien perusteella JasperGold vähentää RTL-koodin tehtävien muutosten määrää vuon loppuvaiheessa jopa 80 prosenttia. Suunnittelun koosta riippuen RTL-koodi saadaan simulaattoriin jopa neljä viikkoa nopeammin. Tämä on merkittävä säästö, kun monet suunnittelut halutaan saada piille mahdollisimman nopeasti, jopa vuoden sisällä työn aloittamisesta, Cadence kertoi.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.