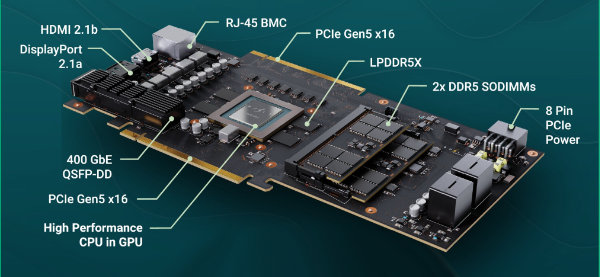

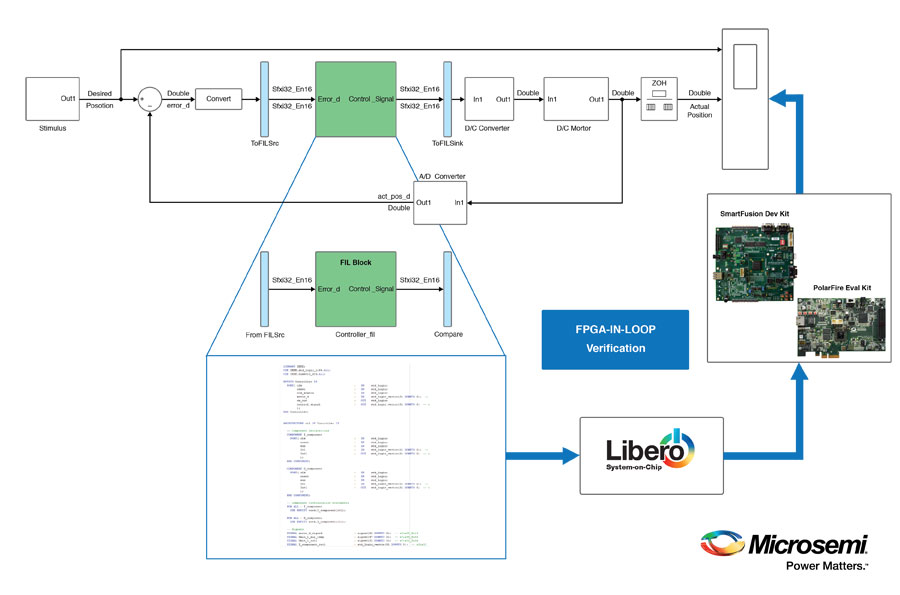

Perinteisesti FPGA-piirejä on koodattu HDL-kuvauskielillä ja tuotos on mapattu verkkolistaksi FPGA-valmistajan toimittamalla suunnittelutyökalulla. Microsemi ja Mathworks ovat nyt ryhtyneet yhteistyöhön helpottaakseen FPGA-piirien algoritmien kehitystä ja testausta.

Yhteistyön myötä Mathworksin HDL Coder- ja HDL Verifier -työkaluja voidaan käyttää generoimaan testejä SmartFusion2- ja PolarFire-sarjan FPGA-piirien VHDL- ja Verilog-kuvauksille. Yritykset kutsuvat uutta suunnitteluvuota nimellä FIL eli Field Programmable Gate Array-in-the-loop.

Microsemin asiakkaat voivat integroida FPGA-kehitysympäristöön sekä MATLAB- että Simulink-työkalut. Tämän ansiosta FPGA-piireille voidaan kehittää algoritmeja graafisesti MATLAB-työkaluilla ja tuotoksia voidaan simuloida Simulinkillä. Tuloksia voidaan tarkastella sekä MATLABissa että Simulinkissä.

Suunnittelijan näkökulmasta FPGA-kehitys onnistuu entiseen tapaan Microsemin Libero-ympäristössä. Siitä vain voidaan jatkoa kutsua MATLAB- ja Simulink-toimintoja. Tavoitteena on löytää koodivirheet eli bugit aikaisemmassa vaiheessa suunnitteluprosessia.

Yhteistyö on ensimmäinen, jossa Mathworksin työkalut on liitetty suoraan FPGA-suunnittelun työkaluihin.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.