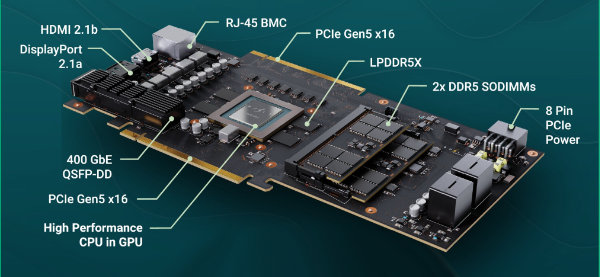

PCIe-väylän 3.0-versiota on käytetty tietotekniikassa jo pitkään, aina vuodesta 2011 asti. Alun perin väylässä piti siirtyä nelospolveen jo vuonna 2013, mutta standardi valmistui vasta tänä vuonna. Seuraavaan eli 5.0-versioon siirrytään jo ensi vuonna.

PCIe 4.0 yltää 16 gigaoperaatioon (GT, gigatransfers) sekunnissa. 5.0-versio kaksinkertaistaa tämän, joten parin vuoden sisällä PCI-väylän nopeus tulee nelinkertaistumaan. Voi myös olla, että väylän 4.0-version elää jää lyhytaikaiseksi.

Laitevalmistajien kannalta uuden väylän käyttöönotto on tietenkin varsin mutkikas prosessi. EDA-talo Cadence Design Systems on nyt ensimmäisenä tuonut tarjolle verifiointi-IP:n, joka tukee tulevaa 5.0-versiota.

Verifiointi-IP:n avulla laitevalmistaja voi varmistaa, että suunnittelun väylä tukee PCI-SIG-järjestön tulevaa standardia. Näin voidaan vakuuttua siitä, että oma tallennusjärjestelmä tai palvelin toimii standardissa määritellyllä tavalla.

PCIe:n 5.0-versio ei tietenkään ole vielä valmis. Se tulee alustavien suunnitelmien mukaan koodaamaan dataa 128/130-bittisesti. Parhaimmillaan dataa siirtyy järjestelmään 128 gigatavua sekunnissa. Yhdellä linjalla (johtimella) dataa siirtyisi neljä gigatavua sekunnissa eli nykyisistä nopeimmista x16-tyyppisistä PCIe-liitännöistä nopeus kasvaa nelinkertaiseksi.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.