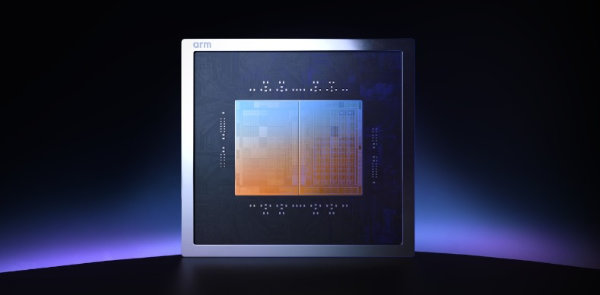

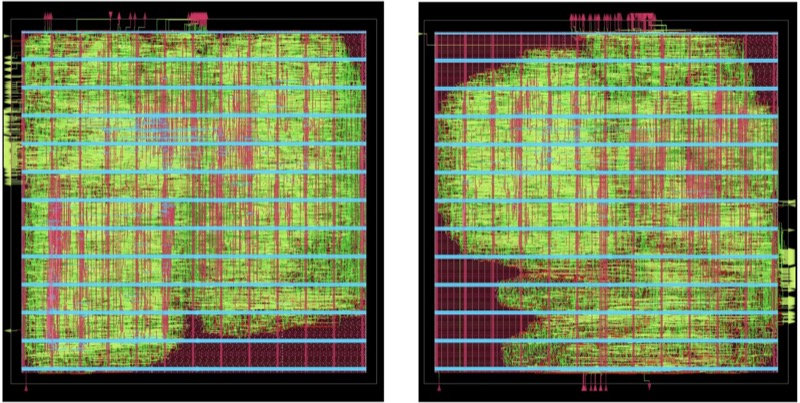

Piirisuunnittelun automaatio otti ison askeleen eteenpäin, kun yhdysvaltalainen startup Verkor syötti 219 sanan vaatimusmäärittelyn AI-agentille – ja sai 12 tunnissa ulos valmiin RISC-V-prosessorin GDSII-tiedostona. Tuloksena syntynyt Vercore-ydin ei vielä kilpaile nykypiirien kanssa, mutta osoittaa, että kokonainen CPU voidaan suunnitella pitkälti ilman ihmistä.

Verkorin kehittämä Design Conductor -työkalu (DC) hoiti koko suunnitteluketjun RTL-moduuleista testipenkkien generointiin ja integraatiotestaukseen asti. Se ajoi koodia Spike ISA -simulaattorissa, debugasi virheitä, analysoi timing-raportteja ja teki tarvittaessa arkkitehtuurimuutoksia. Käytännössä agentti teki sen, mihin perinteisesti tarvitaan tiimi suunnittelijoita ja EDA-työkaluja.

AI ei tyytynyt yhteen ratkaisuun, vaan generoi ja vertaili useita mikroarkkitehtuureja. Tuloksena oli muun muassa suorituskykyyn ja energiatehokkuuteen optimoidut versiot. Lopullinen Vercore on viisiportaisella pipeline-rakenteella toteutettu RV32I-ydin, jossa on tuki Zmmul-laajennukselle.

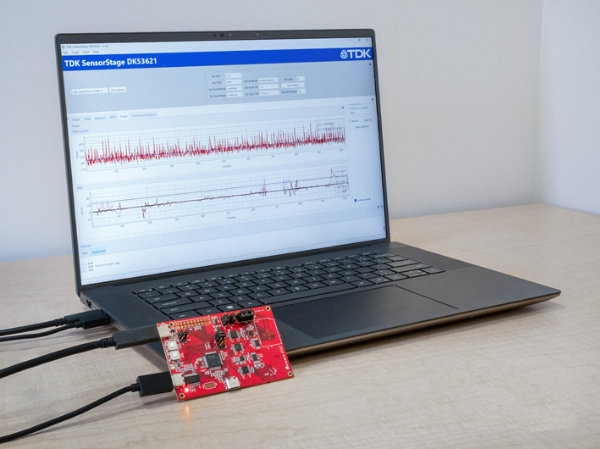

Suorituskyvyltään Vercore jää kuitenkin selvästi jälkeen nykyprosessoreista. Sen kerrotaan yltävän 1,48 gigahertsin kellotaajuuteen 7 nanometrin prosessissa ja noin 3261 CoreMark-pisteeseen. Tämä vastaa suunnilleen Intelin Celeron SU2300 -prosessoria vuodelta 2011.

Mielenkiintoista on, että AI pystyi myös timing-optimointiin, joka on yksi perinteisen piirisuunnittelun vaikeimmista osa-alueista. Verkor kokeili lisäksi 13-portaista out-of-order-arkkitehtuuria, ja agentti kykeni ratkaisemaan sekä toiminnallisia että ajoitukseen liittyviä ongelmia myös tässä monimutkaisemmassa rakenteessa.

Täydellinen automaatio ei kuitenkaan ole vielä todellisuutta. Kehittäjien mukaan suunnittelu vaatisi edelleen merkittävää käsityötä ennen tuotantoon viemistä. AI kärsii samoista ongelmista kuin suuret kielimallit yleensä: se ei aina optimoi ilman erillistä ohjausta ja tekee virheitä, jotka vaativat ihmisen korjauksia.

Lisäksi työkalulla on puutteita, jotka liittyvät erityisesti laitteistosuunnitteluun. Se käsittelee Verilogia paikoin kuin perinteistä sekventiaalista ohjelmointikieltä, vaikka kyse on tapahtumapohjaisesta kuvauksesta. Tämä voi johtaa virheellisiin suunnitteluratkaisuihin ilman tarkkaa ohjausta.

Silti suunta on selvä. Kun AI pystyy jo nyt suunnittelemaan kokonaisen CPU:n vuorokaudessa, seuraava kehitysaskel on laadun, optimoinnin ja tuotantovalmiuden parantaminen. Jos tämä onnistuu, vaikutus piirisuunnittelun tuottavuuteen voi olla dramaattinen.

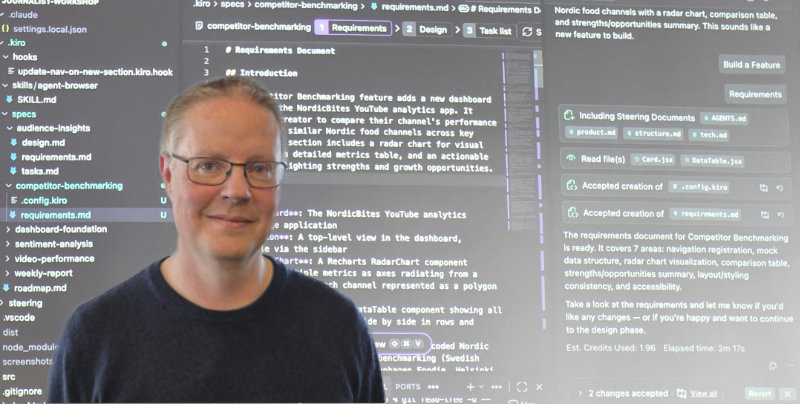

Jan Tångring, Elektroniktidningen