Stratix on Intelin FPGA-piirien lippulaivaperhe. Nyt yhtiö on ryhtynyt toimittamaan näytteitä uudesta Stratix 10 -piiristä, jolla on peräti 3,7 kertaa enemmän logiikkaelementtejä kuin yhtiön tähän asti tiheimmällä ohjelmoitavalla piirillä.

Stratix on Intelin FPGA-piirien lippulaivaperhe. Nyt yhtiö on ryhtynyt toimittamaan näytteitä uudesta Stratix 10 -piiristä, jolla on peräti 3,7 kertaa enemmän logiikkaelementtejä kuin yhtiön tähän asti tiheimmällä ohjelmoitavalla piirillä.

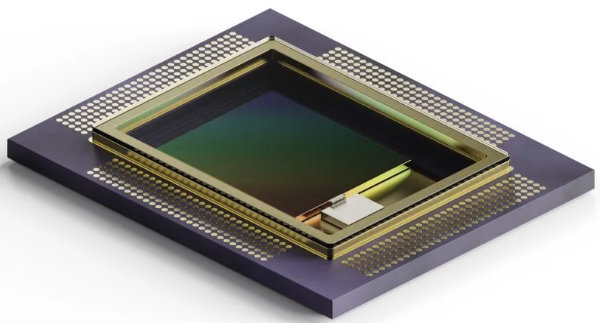

Maailman tihein ohjelmoitava piiri on vaatinut Inteliltä eräänlaisen taikatempun. Piiri on käytännössä kaksi suurta FPGA-sirua, jotka on yhdistetty toisiinsa Intelin omalla EMIB-väylällä (Embedded Multi-Die Interconnect Bridge). Niillä molemmilla on 5,1 miljoonaa logiikkaelementtiä, joten yhteensä LE-yksiköitä tulee massiiviset 10,2 miljoonaa.

Intelin mukaan Stratix 10 GX 10M -piirejä tullaan tarvitsemaan erityisesti suurten ASIC-piirien protokehityksessä ja emulointijärjestelmissä. Emulaattoreita kehittää moni valmistaja ja niille entistä tiheämpi FPGA-piiri tuo entistä enemmän suorituskykyä.

Moni puolijohdevalmistaja käyttää FPGA-pohjaisia emulaattorijärjestelmiä suurimpien piiriensä kehittämisessä ja niiden toiminnan varmentamisessa eli verifioinnissa. Intel tekee näin tietysti itsekin omien Core- ja muiden piiriensä kanssa.

FPGA-piirejä käytetään myös esimerkiksi algoritmien kehitykseen, aikaisen vaiheen ohjelmistonkehitykseen SoC-kehityksessä ja RTOS-verifioinnissa.

FPGA-valmistajat kisaavat edelleen ennätyslukemista lippulaivapiireissään. Xilinx esitteli itse elokuussa 8,9 miljoonan logiikkaelementin jättipiirin, mutta nyt vanha kilpakumppani Altera siis nokittaa Intelin nimen alla.