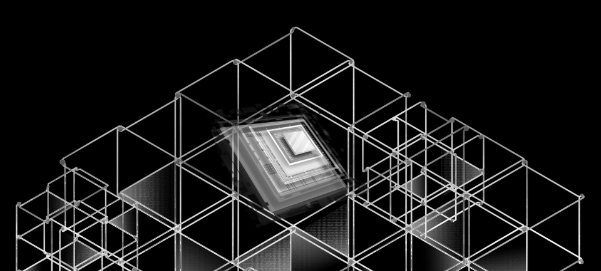

Piirien valmistuksen siirtyminen yhä tiheämpiin prosesseihin tuo huomattavasti etua digitaaliosiin. Nopeus kasvaa ja tehonkulutus pienenee. Samaan aikaan geometrioiden kutistaminen aiheuttaa isoja ongelmia järjestelmäpiirien analogiaosien suunnitteluun.

Piirien valmistuksen siirtyminen yhä tiheämpiin prosesseihin tuo huomattavasti etua digitaaliosiin. Nopeus kasvaa ja tehonkulutus pienenee. Samaan aikaan geometrioiden kutistaminen aiheuttaa isoja ongelmia järjestelmäpiirien analogiaosien suunnitteluun.

Siemens Digital Indsutriesin AMDS Verification -ryhmän tuotemarkkinointia vetävän Greg Curtisin mukaan siirtyminen tiheämpiin prosesseihin tarkoittaa, että pelkkä analogiaosan simulointi ilman, että parasiittiset ilmiöt otetaan huomioon, ei enää kestä. – Tästä sijoittelun jälkeisestä simuloinnista (PLS, post layout simulation) tulee analogiaosien verifioinnin pullonkaula.

Curtisin mukaan tämä johtaa siihen, että tuotantokustannukset kasvavat, parasiittisten ilmiöiden määrä piireillä kasvaa, variabiliteetti kasvaa, resistanssi kasvaa. – Kun samalla piirirakenteet monimutkaistuvat ja siirrytään pois tasomaisista rakenteista erilaisiin 3D FinFET -arkkitehtuureihin, simulointiin kuluu jatkuvasti enemmän aikaa.

Tämä kaikki uhkaa analogiasuunnittelun saamista valmiiksi ajoissa. Tarvitaan tarkempi analoginen malli suunnittelusta, jotta uudet tuotteet saadaan nopeammin markkinoille.

Siemensin eli entisen Mentorin ratkaisu ongelmaan on uusi Analog FastSPICE eXTreme -työkalu. ALS-alustan päivitys on tuonut mukaan nopeamman SPICE-matriisimoottorin ja uusia RC-algoritmeja. Curtisin mukaan analogiaosien verifiointi nopeutuu merkittävästi uusien ominaisuuksien myötä. Esimerkiksi PLL-osan verifiointi nopeutuu 6-kertaisesti ja radiovastaanottimen jopa 15-kertaisesti. – Simulointi nopeuttaa aina vähintään 3-kertaisesti, Curtsi kehuu.

Vanhoille AFS-käyttäjille uusi versio tulee ilman lisäkustannuksia. Uutta työkalua on kehitetty early access -asiakkaiden kanssa vuoden alusta lähtien. Lähtökohtana oli alusta asti SPICE-tason tarkkuuden säilyttäminen ja simuloinnin nopeuttaminen.

ETN:n digitaalinen aikakauslehti ETNdigi 1/2026 on julkaistu. Uusi numero kokoaa yhteen elektroniikka-alan keskeisiä teknologiateemoja kvanttilaskennasta ja tekoälystä energiatehokkaaseen tehoelektroniikkaan, IoT-järjestelmiin ja ajoneuvojen latausinfrastruktuuriin.

ETN:n digitaalinen aikakauslehti ETNdigi 1/2026 on julkaistu. Uusi numero kokoaa yhteen elektroniikka-alan keskeisiä teknologiateemoja kvanttilaskennasta ja tekoälystä energiatehokkaaseen tehoelektroniikkaan, IoT-järjestelmiin ja ajoneuvojen latausinfrastruktuuriin.

Nokian toimitusjohtaja Justin Hotard arvioi yhtiön Yhdysvaltain arvopaperimarkkinavalvoja SEC:lle toimittamassa Form 20-F 2025 -vuosiraportissa, että mobiiliverkkomarkkina ei ole lähivuosina varsinainen kasvuala. Hänen mukaansa markkinan odotetaan pysyvän lähinnä vakaana samalla kun Nokia keskittyy parantamaan liiketoiminnan kannattavuutta.

Nokian toimitusjohtaja Justin Hotard arvioi yhtiön Yhdysvaltain arvopaperimarkkinavalvoja SEC:lle toimittamassa Form 20-F 2025 -vuosiraportissa, että mobiiliverkkomarkkina ei ole lähivuosina varsinainen kasvuala. Hänen mukaansa markkinan odotetaan pysyvän lähinnä vakaana samalla kun Nokia keskittyy parantamaan liiketoiminnan kannattavuutta.