Tällä hetkellä tihein kaupallinen puolijohteiden valmistustekniikka on TSMC:n ja Samsungin 5 nanometrin prosessi. Samsung on jo näyttänyt seuraavaa sukupolvea piiritekniikan ISSCC-konferenssissa. Tuloksena oli kolmen nanometrin demopiiri.

Tällä hetkellä tihein kaupallinen puolijohteiden valmistustekniikka on TSMC:n ja Samsungin 5 nanometrin prosessi. Samsung on jo näyttänyt seuraavaa sukupolvea piiritekniikan ISSCC-konferenssissa. Tuloksena oli kolmen nanometrin demopiiri.

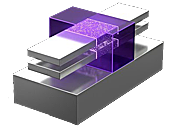

Tämän hetken edistyneimmissä piireissä transistorit rakennetaan FinFET-rakenteella. Fin viittaa hainevämäiseen muotoon, jolla lähde ja nielu nousevat ylös piin pinnasta. Rakenne on ollut hallitseva 14 ja 10 nanometrin prosesseista lähtien.

10 nanometrissä rakenne alkoi jo tuottaa ongelmia jännitevuotojen takia. Rakennetta paranneltiin niin, että transistori rakennettiin nanolangoilla. Näiden avulla voitiin paremmin hallita virrankulkua hilassa. Rakennetta kutsutaan nimellä GAAFET (gate-all-around field-effect transistors).

Alle viidessä nanometrissä tämäkin rakenne ajautuu FinFETin kaltaisiin ongelmiin. Sen takia sekä TSMC että Samsung ovat kehittäneet MBCFET-rakenteen (Multi-Bridge Channel FET), jossa nanolangat korvataan nanokalvoilla.

Samsungin mukaan rakenne tulee kaupallisesti tarjolle jo 3 nanometrin piireissä. Yhtiön mukaan nanokalvon leveys määrittelee transistorin ominaisuudet: leveämpi nanokalvo nostaa suorituskykyä eli transistoria voidaan ajaa suuremmalla virralla. Eri käyttötarkoituksiin nanokalvoa voidaan viritellä.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.

– Haluamme olla tekoälyn hyödyntämisen edelläkävijöitä, ja se vaatii luottamuksen rakentamista asiakkaiden suuntaan. Pelkkä yrityksen oma lupaus ei enää riitä, sanoo Julius Manni. Vincit on saanut ensimmäisenä Suomessa akkreditoidun ISO/IEC 42001 -sertifikaatin.