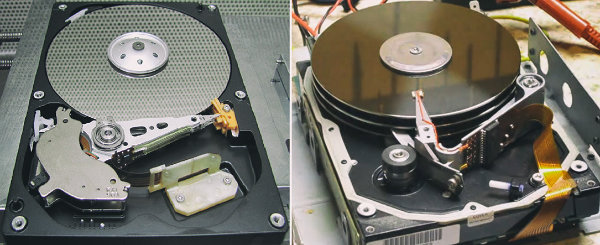

FPGA-piirien valmistaja Altera ja sen piirien tuotannosta vastaavan taiwanilainen TSMC sanovat tuovansa uuden kotelotekniikan Alteran siruille. Uusi kuparinystyjä hyödyntävä tekniikka lisää sekä piirien luotettavuitta että suorituskykyä.

Perinteisiin kuparinystyihin verrattuna TSMC:n kehittämä ja patentoitu tekniikka mahdollistaa liitinnystyjen valmistamisen hyvin tiheästi, alle 150 mikronin päähän toisistaan.

Altera on ensimmäinen TSMC:n kumppani, joka ottaa uuden tekniikan kaupalliseen käyttöön. Sitä hyödynnetään jo Alteran uusissa 20 nanometrin prosessissa valmistetuissa siruissa ja tullaan käyttämään yhtiön tuleville SoC-piireillä.

FPGA-piirejä käytetään usein erittäin nopeissa tietoliikennepiireissä, joissa linkkien toteuttaminen vaatii paljon nopeita liitäntöjä. Siksi aiempaa tihempi liitinrakenne auttaa juuri FPGA-piireissä.

TSMC:n mukaan uusi kotelo sopii erityisesti suurikokoisten ja nopeita liitäntöjä edellyttävien suunnittelujen kotelointiin. Yhtiön mukaan uusi kotelo yltää jo nyt tuotannossa 99,8 prosentin saantoon, mikä on erittäin hyvä lukema.

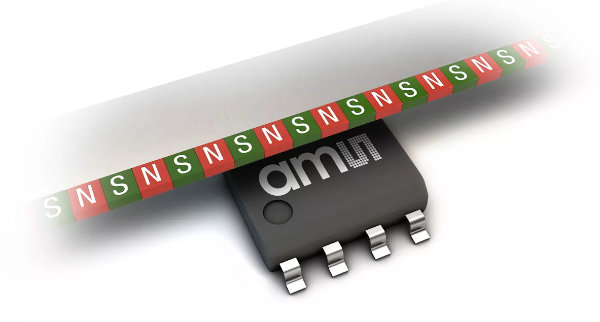

Virtaamamittaus on monissa laitteissa kriittinen mutta usein ongelmallinen toiminto. Perinteiset mekaaniset anturit kuluvat ja jäävät sokeiksi pienille virtausnopeuksille. Ultraäänitekniikkaan perustuvat valmiit moduulit tarjoavat nyt tarkan, huoltovapaan ja helposti integroitavan vaihtoehdon niin kuluttaja- kuin teollisuussovelluksiin.

Virtaamamittaus on monissa laitteissa kriittinen mutta usein ongelmallinen toiminto. Perinteiset mekaaniset anturit kuluvat ja jäävät sokeiksi pienille virtausnopeuksille. Ultraäänitekniikkaan perustuvat valmiit moduulit tarjoavat nyt tarkan, huoltovapaan ja helposti integroitavan vaihtoehdon niin kuluttaja- kuin teollisuussovelluksiin.